traps to

location

X

'

42

1

as a result

of

impending overflow

or

underflow

of

the word

count

(SPD

49-63)'

as follows:

TW

Word

count

overflow/underflow

action

o

If

the

execution

of

a push instruction would cause

the

word

count

to

exceed

2

15

-1,

or if

the

execution

of

a pull instruction would cause

the

word

count

to be

less than 0, the

basic

processor traps to

location

X

'

42

1

with the condition

code

unchanged.

Instead

of

trapping to

location

X'421, the

basic

pro-

cessor sets CC3 to 1 and then

executes

the

next

instruction in

sequence.

PUSH-DOWN

CONDITION

CODE

SETTINGS

If the

execution

of

a push-down instruction is

attempted

and the basic processor traps to

location

X'421, the

condi-

tion

code

remains unchanged from

the

value

it

contained

immediately before the instruction was

executed.

If

the

execution

of

a push-down instruction is

attempted

and

the instruction

is

aborted

because

of

impending

stack

limit

overflow

or

underflow (or both)

but

the

push-down

stack

limit trap is

inhibited

by one (or both)

of

the inhibits

(TS

and TW),

then,

CC 1

or

CC3

is

set

to 1 (or both

are

set

to

lis)

to

indicate

the

reason for aborting the push-down

instruction, as

follows:

o

2 3 4 Reason for

abort

- 0

Impending overflow

of

word

count

on a push

operation

or impending underflow

of

word

count

on a pull

operation.

The push-down

stack

limit trap was

inhibited

by

the

TW

bit

(SPD4S).

Impending overflow

of

space

count

on a pull

operation

or

impending underflow

of

space

count

on a push

operation.

The push-down

stack

limit trap was

inhibited

by

the

TS

bit

(SPDJ2)·

Impending overflow

of

word

count

and

under-

flow

of

space

count

on a push

operation

or

im-

pending overflow

of

space

count

and

underflow

of

word

count

on a pull

operation.

The

push-

down

stack

limit trap was

inhibited

by both

the

TW

and the

TS

bits.

If

a push-down instruction is successfully

executed,

CCl

and CC3

are

reset to 0

at

the

completion

of

the instruction.

Also,

CC2 and CC4

are

independently

set

to indi

cate

the

current

status

of

the

space

count

and

the

word

count,

respectively,

as follows:

2 3 4 Status

of

space

and

word counts

-

0 - 0 The

current

space

count

and

the

current word

count

are

both

greater

than

zero.

o The

current

space

count

is

greater

than

zero,

but

the

current

word

count

is

zero,

indicating

that

the

stack

is now empty.

If

the

next

oper-

ation

on

the

stack

is a pull instruction, the

instruction wi

II

be

aborted.

- 0 The

current

word

count

is

greater

than

zero,

but

the

current

space

count

is

zero,

indicating

that

the

stack

is now fu II. If the

next

opera-

tion on the

stack

is a push instruction, the

instruction wi

II be

aborted.

If

the

basic

processor does

not

trap to

location

X

I

42

1

as a

result

of

impending

stack

limit

overflow/underflow,

CC2

and

CC4

indicate

the

status

of

the

space

and

word counts

at

the

termination

of

the

push-down instruction, regardless

of

whether

the

space

and

word counts

were

actually

modi-

fied by

the

instruction.

In

the following descriptions

of

the push-down instructions,

condition

code

settings

given

are

only

those

that

can

be produced by the instruction,

provided

that

the

basic processor does

not

trap to

lo-

cation

X1421.

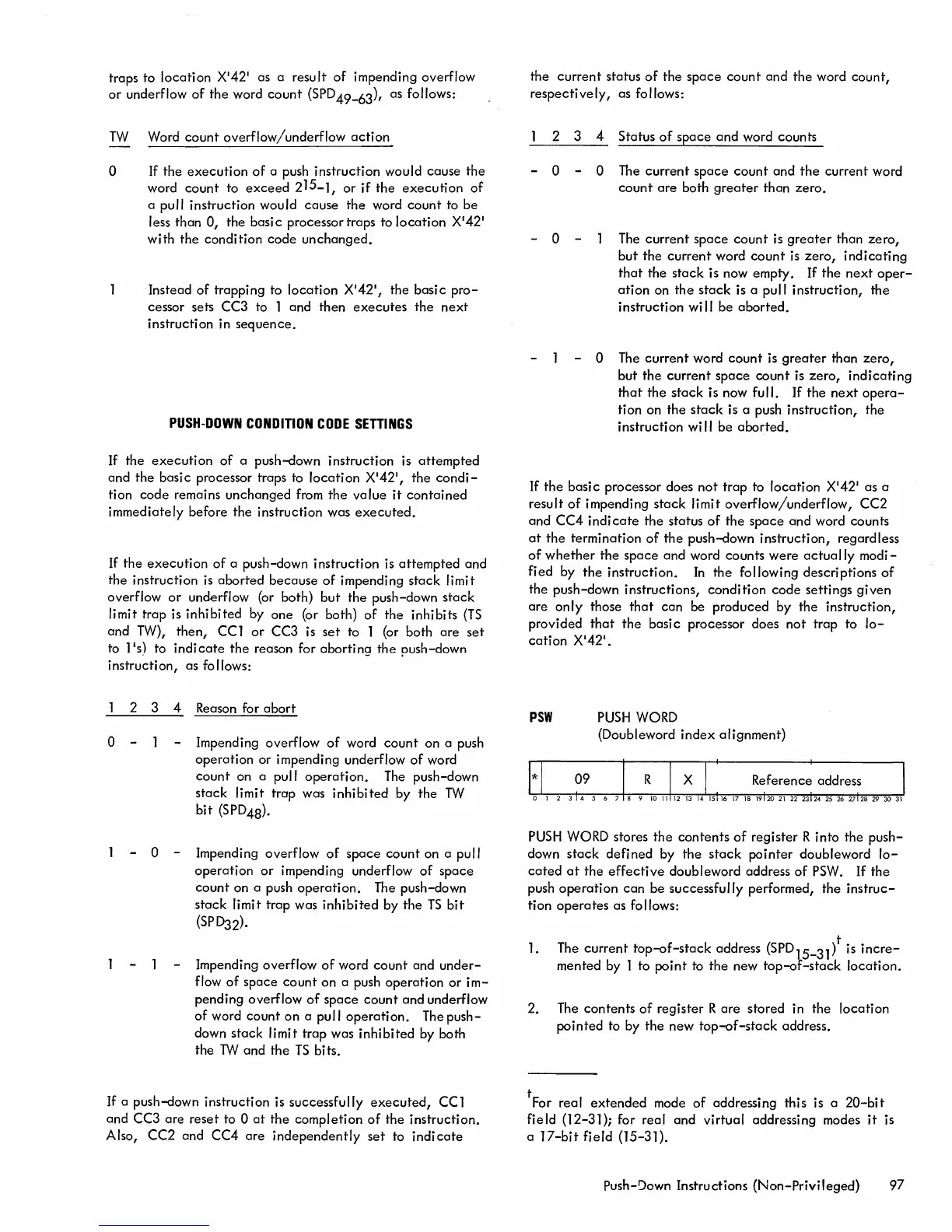

PSW

PUSH

WORD

(Doubleword

index

alignment)

PUSH

WORD stores

the

contents

of

register R into the

push-

down

stack

defined

by the

stack

pointer

doubleword

lo-

cated

at

the

effective

doubleword address

of

PSW.

If

the

push

operation

can

be successfully performed, the

instruc-

tion

operates

as follows:

1.

The

current

top-of-stack

address

(SPD

15

_

31

)t is

incre-

mented by 1 to

point

to the new

top-of-stack

location.

2. The

contents

of

register R

are

stored in the location

pointed

to by the new

top-of-stack

address.

t

For real

extended

mode

of

addressing this is a

20-bit

field (12-31); for real and virtual addressing modes

it

is

a

17-bit

field

(15-31).

push-I)own Instructions

(Non-Privileged)

97

Loading...

Loading...