Bits

0-24

of

register 1

are

cleared

and the remaining

count

is loaded into bits

25-31.

If the

initial

contents

of

bit

0

is

equal

to

I,

then no bits

are

shifted by the instruction.

In

this

case

the

original

count

in the instruction

is

stored

in register 1.

Searching

shift causing a

change

in

bit

position 0 causes

CC2

to be

set

to 1. If

bit

position 0 is not changed during

a searching shift,

CC2 is

cleared.

CC4

is

set

to 1

if

the

shift

is

terminated with a 1 in

bit

position

O.

Affected:

(R),

(Rl), CC2,

CC4

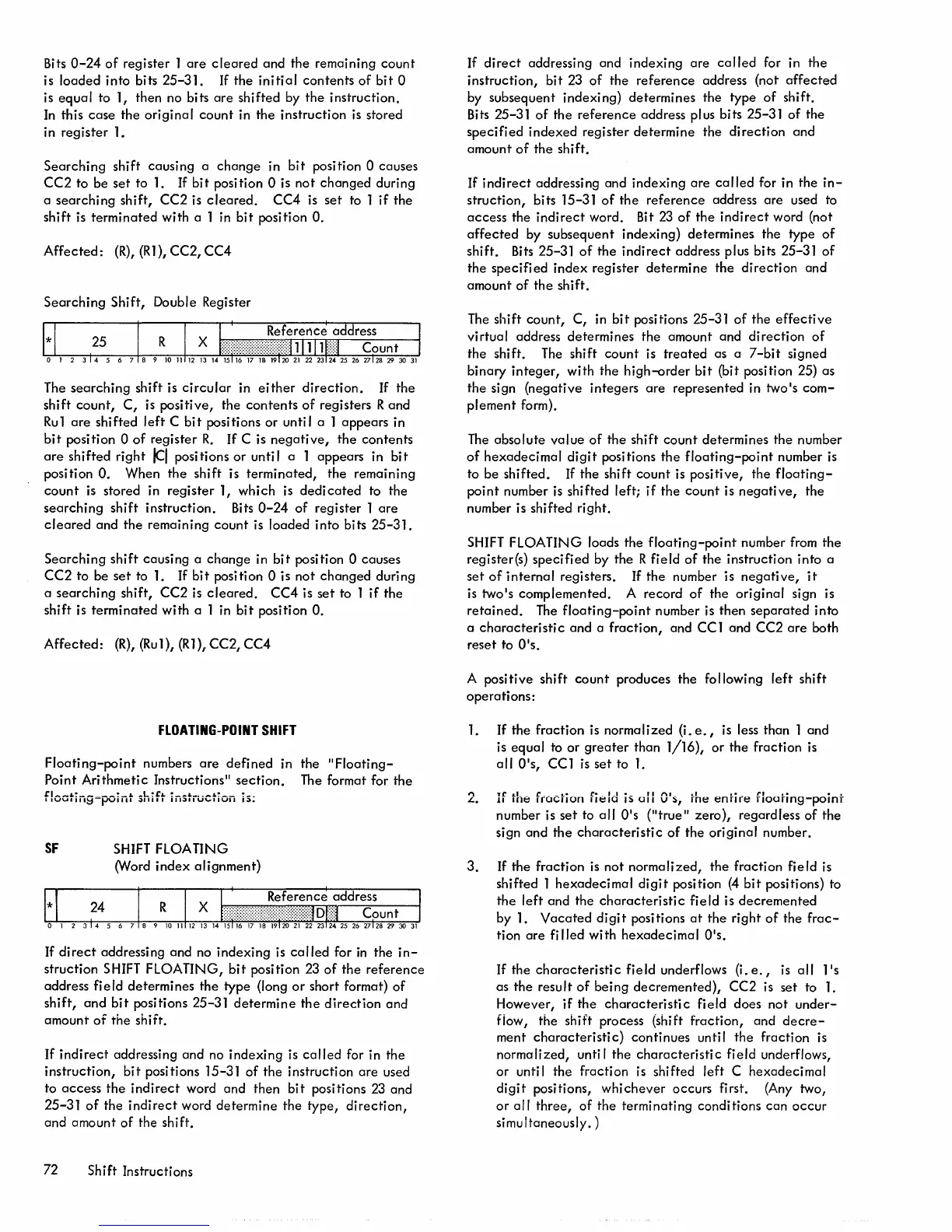

Searching

Shift, Double Register

The

searching

shift is

circular

in

either

direction.

If the

shift

count,

C,

is

positive, the

contents

of

registers

Rand

Rul

are

shifted

left

C

bit

positions or until a 1 appears in

bit

position 0

of

register

R.

If

C is

negative,

the

contents

are

shifted right

lei

positions

or

unti I a 1 appears in

bit

position

O.

When the shift is terminated, the remaining

count

is stored in register

I,

which is

dedicated

to the

searching

shift instruction.

Bits

0-24

of

register 1

are

cleared

and

the remaining

count

is loaded into bits

25-31.

Searching

shift

causing a

change

in

bit

position 0 causes

CC2

to be

set

to 1.

If

bit

position 0 is not changed during

a

searching

shift, CC2

is

cleared.

CC4

is

set

to 1

if

the

shift

is

terminated with a 1 in

bit

position

O.

Affected:

(R),

(Rul), (Rl), CC2, CC4

FLOATING-POINT

SHIFT

Floating-point

numbers

are

defined in the IIFloating-

Point Arithmetic Instructions

ll

section.

The format for the

&I~_":

_____

:_,,

_L:C"

:

__

L_

••

_":

__

:

__

IIV,",III'~-tJVlIlI

~'IIII

II'~IIU"""VII

,~;

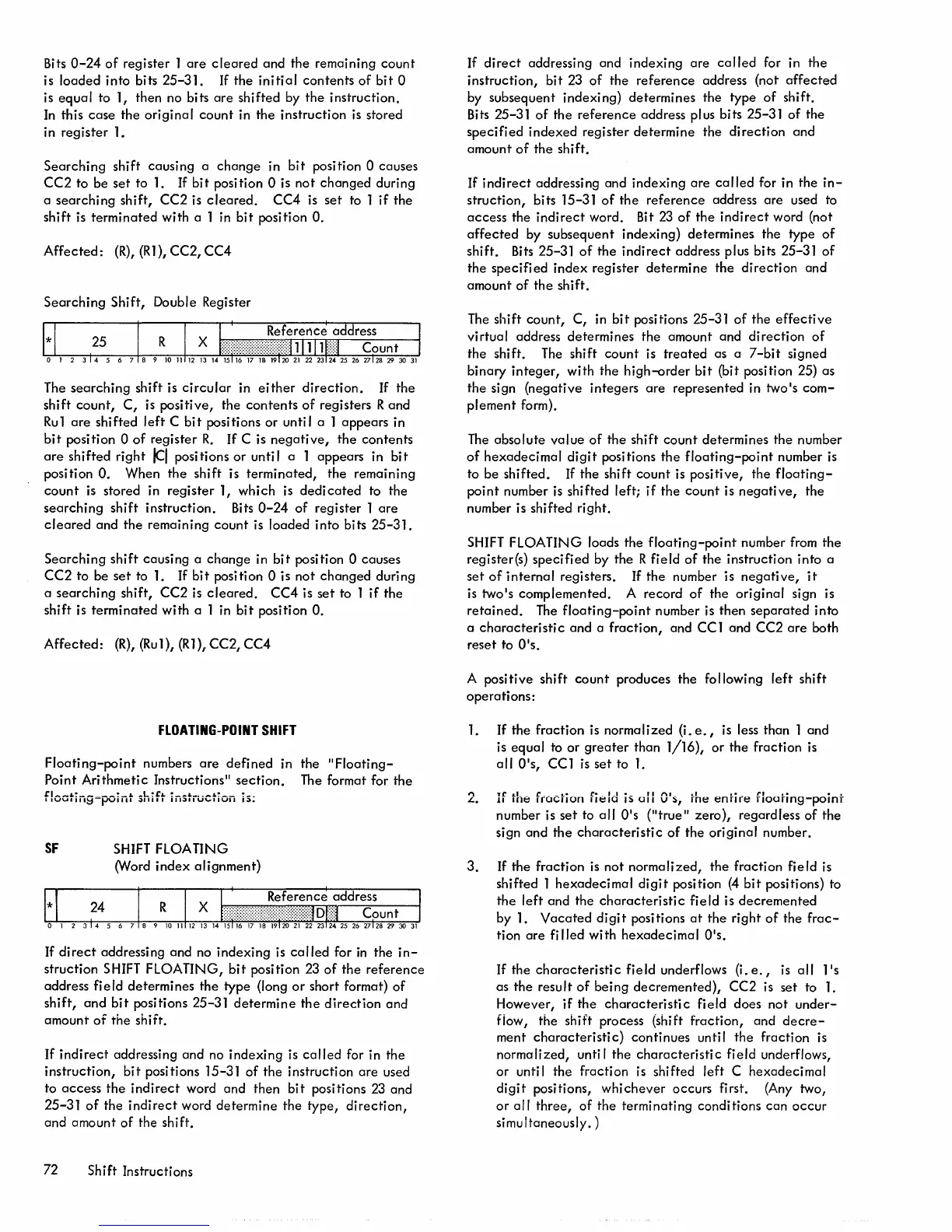

SF

SHIFT FLOATING

(Word

index

alignment)

If

direct

addressing and no indexing

is

called

for

in

the

in-

struction

SHIFT

FLOATING,

bit

position 23

of

the

reference

address

field

determines the type (long

or

short format)

of

shift,

and

bit

positions 25-31

determine

the

direction

and

amount

of

the shift.

If

indirect

addressing and no indexing is

called

for in the

instruction,

bit

positions 15-31

of

the instruction

are

used

to

access

the

indirect

word and then

bit

positions

23

and

25-31

of

the

indirect

word determine the type,

direction,

and amount

of

the shift.

72

Shift Instructions

If

direct

addressing and indexing

are

called

for in the

instruction,

bit

23

of

the

reference

address (not

affected

by subsequent indexing) determines the type

of

shift.

Bits

25-31

of

the

reference

address plus bits 25-31

of

the

specified

indexed register determine the

direction

and

amount

of

the shift.

If

indirect

addressing and indexing

are

called

for in the

in-

struction, bits 15-31

of

the

reference

address

are

used to

access

the

indirect

word. Bit

23

of

the

indirect

word (not

affected

by subsequent indexing) determines the type

of

shift.

Bits

25-31

of

the

indirect

address plus bits 25-31

of

the specified index register determine the

direction

and

amount

of

the shift.

The shift

count,

C, in

bit

positions 25-31

of

the

effective

virtual address determines the amount and

direction

of

the shift.

The

shift

count

is

treated

as a

7-bit

signed

binary

integer,

with the

high-order

bit

(bit position 25) as

the sign (negative integers

are

represented in two's

com-

plement form).

The

absolute value

of

the shift

count

determines the number

of

hexadecimal

digit

positions the

floating-point

number

is

to be shifted.

If

the shift

count

is

positive, the

floating-

point number is shifted left;

if

the

count

is

negative,

the

number is shifted right.

SHIFT

FLOATING loads the

floating-point

number from the

register(s)

specified

by the R field

of

the instruction into a

set

of

internal

registers. If the number is

negative,

it

is twols complemented. A record

of

the original sign is

retained.

The

floating-point

number is then

separated

into

a

characteristic

and a

fraction,

and

CCI

and CC2

are

both

reset to

OIS.

A positive shift

count

produces the following left shift

operations:

1. If the fraction is normalized (i.

e.,

is less than 1 and

is equal to or

greater

than

1/16),

or

the fraction

is

all

OIS,

CCl

is

set

to

1.

,..

1'1:

LL

_

r.

__

_

L-

r-.

'.1

-_

II

"....

••

rl

.-

L.

11

HIt::

IrU~lIon

rlt::IU

I:>

UII

V:>,

rn~ enflr~

flouflng-polnT

number is

set

to

all

OIS

(lltrue

ll

zero), regardless

of

the

sign and the

characteristic

of

the original number.

3.

If the fraction

is

not

normalized, the fraction field

is

shifted 1 hexadecimal

digit

position

(4

bit

positions) to

the left and the

characteristic

field is decremented

by 1.

Vacated

digit

positions

at

the right

of

the

frac-

tion

are

fi

lied with hexadecimal

OIS.

If

the

characteristic

field underflows

(i.e.,

is

all

lis

as the result

of

being decremented), CC2 is set to 1.

However,

if the

characteristic

field does not

under-

fiow, the shift process (shift

fraction,

and

decre-

ment

characteristic)

continues until the fraction is

normalized, unti

I the

characteristic

field underflows,

or

unti I the fraction

is

shifted left C hexadecimal

digit

positions,

whichever

occurs first. (Any two,

or

all

three,

of

the terminating conditions can

occur

simultaneously. )

Loading...

Loading...