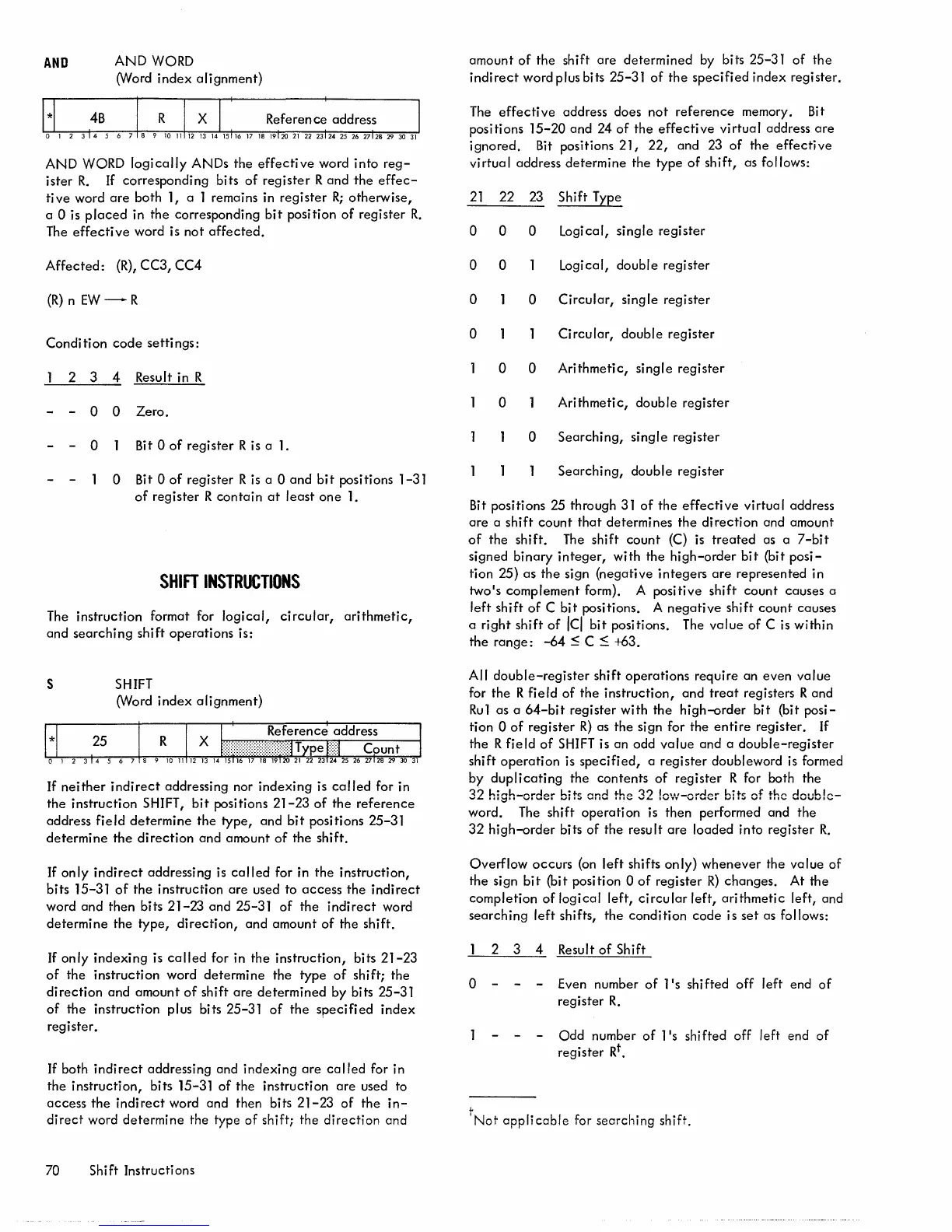

AND

AND

WORD

0Nord

index

alignment)

AND

WORD

logically

ANDs the

effective

word into

reg-

ister

R.

If

corresponding bits

of

register

R and the

effec-

tive

word

are

both 1, a 1 remains in register

R;

otherwise,

a

0 is

placed

in the corresponding

bit

position

of

register

R.

The

effective

word is

not

affected.

Affected:

(R),

CC3, CC4

(R)

n

EW-R

Condition

code

settings:

2 3 4 Result in R

-

0 0 Zero.

-

0 Bit 0

of

register R is a

1.

OBit

0

of

register R

is

a 0

and

bit

positions 1-31

of

register R contain

at

least

one

1.

SHIFT

INSTRUCTIONS

The instruction format for

logical,

circular,

arithmetic,

and

searching

shift operations is:

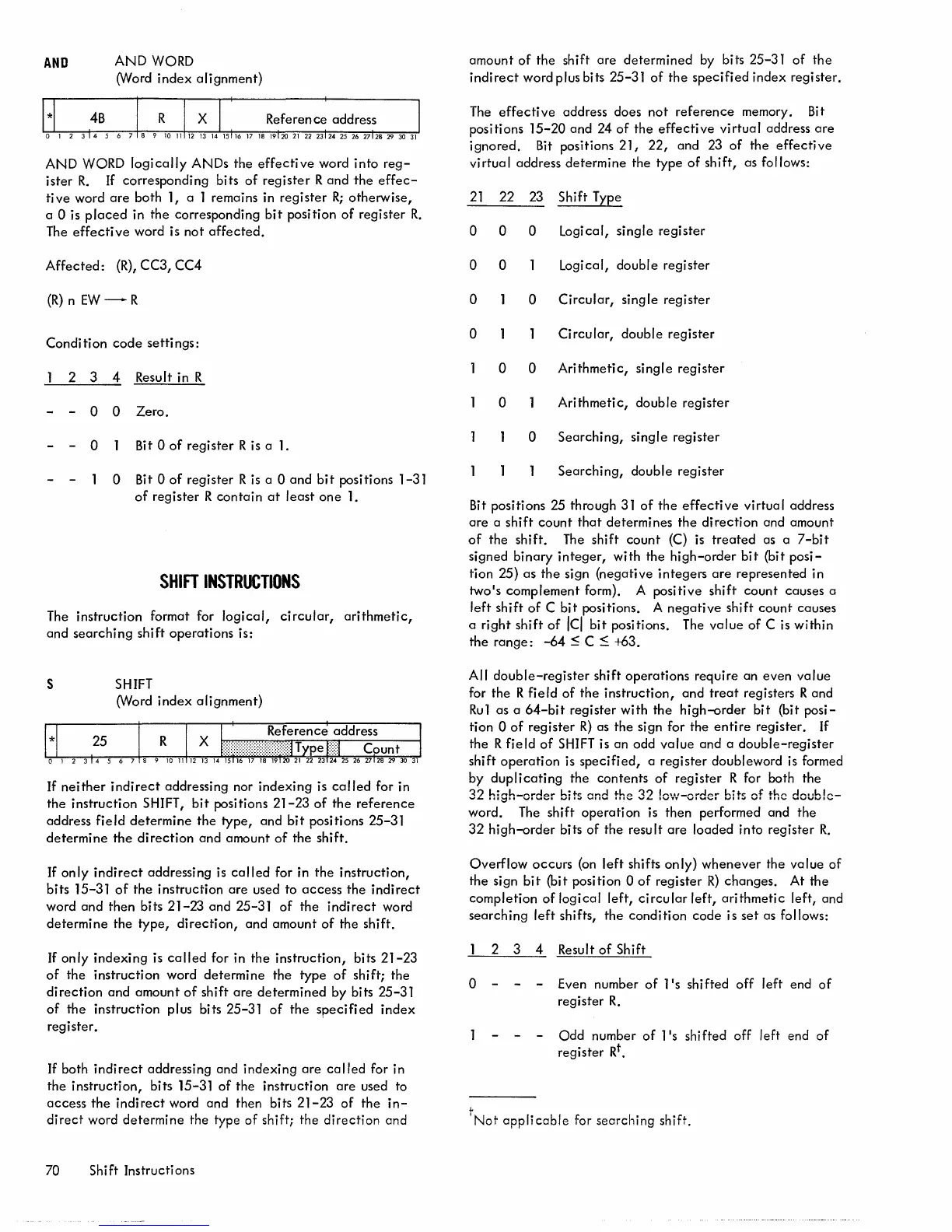

S SHIFT

0Nord

index

alignment)

If

neither

indirect

addressing nor indexing is

called

for in

the instruction

SHIFT,

bit

positions

21-23

of

the

reference

address

field

determine

the type, and

bit

positions 25-31

determine

the

direction

and amount

of

the shift.

If on

Iy

indirect

addressing

is

called

for in

the

instruction,

bits 15-31

of

the

instruction

are

used to

access

the

indirect

word and then bits

21-23

and 25-31

of

the

indirect

word

determine the type,

direction,

and

amount

of

the shift.

If only indexing is

called

for in the instruction, bits

21-23

of

the instruction word determine the type

of

shift; the

direction

and amount

of

shift

are

determined by bits 25-31

of

the instruction plus bits 25-31

of

the

specified

index

register.

If

both

indirect

addressing and indexing

are

called

for in

the instruction, bits 15-31

of

the instruction

are

used to

access

the

indirect

word and then bits

21-23

of

the

in-

direct

word determine the type

of

shift; the

direction

and

70 Shift Instructions

amount

of

the shift

are

determined

by

bits 25-31

of

the

indirect

word plus bits 25-31

of

the

specified

index register.

The

effective

address does

not

reference

memory. Bit

positions

15-20

and 24

of

the

effective

virtual address

are

ignored.

Bit

positions

21, 22,

and 23

of

the

effective

virtual address determine the type

of

shift, as follows:

21

22

23

Shift Type

0 0 0

Logical,

single register

0 0

Logical, double register

0

0

Circular,

single register

0

Circular,

double register

0 0

Arithmetic, single register

0

Arithmetic, double register

0

Searching, single register

Searching, double register

Bit

positions 25 through

31

of

the

effective

virtual address

are

a shift

count

that

determines the

direction

and amount

of

the shift.

The

shift count

(C)

is

treated

as a

7-bit

signed binary

integer,

with the

high-order

bit

(bit

posi-

tion 25) as the sign (negative integers

are

represented in

two's complement form). A positive shift count causes a

left shift

of

C

bit

positions. A

negative

shift count causes

a right shift

of

Ici

bit

positions.

The

value

of

C is within

the

range:

-64

~

C

~

+63.

All

double-register

shift operations require an even value

for the R field

of

the instruction,

and

treat

registers

Rand

Rul

as a

64-bit

register with the

high-order

bit

(bit

posi-

tion 0

of

register

R)

as the sign for the

entire

register. If

the R field

of

SHIFT

is an odd

value

and a

double-register

shift

operation

is

specified,

a register doubleword

is

formed

by

duplicating

the contents

of

register R for both the

32

high-order bits and the

32

!ov/-order b!ts

of

the

doub!c-

word. The shift

operation

is then performed and the

32

high-order

bits

of

the result

are

loaded into register

R.

Overflow occurs

(on

left

shifts only) whenever the value

of

the sign

bit

(bit position 0

of

register

R)

changes. At the

completion

of

logical left,

circular

left,

arithmetic

left, and

searching left shifts, the condition

code

is

set

as follows:

2 3 4 Result

of

Shift

o - Even number

of

l's

shifted

off

left end

of

register

R.

Odd number

of

l's

shifted off left end

of

register

Rt.

t

Not

appli

cable

for searching shift.

Loading...

Loading...