CC1 is

unchanged

by

the

instruction.

CC2

indicates

whether

or

not

the

two

operands

have

lis

in

corre-

sponding

bit

positions, regardless

of

their

arithmetic

relationship.

CC3 and

CC4

are

set

according

to

the

arithmeti

c re lationshi p

of

the

two

operands,

regard

less

of

whether

or

not

the

two

operands

have

lis

in

corre-

sponding

bit

positions. For

example,

if

the

register

operand

is

arithmetically

less than

the

effective

oper-

and,

and

the

two

operands

both

have

lis

in

at

least

one

corresponding

bit

position,

the

condition

code

setting

for

the

comparison

instruction

is:

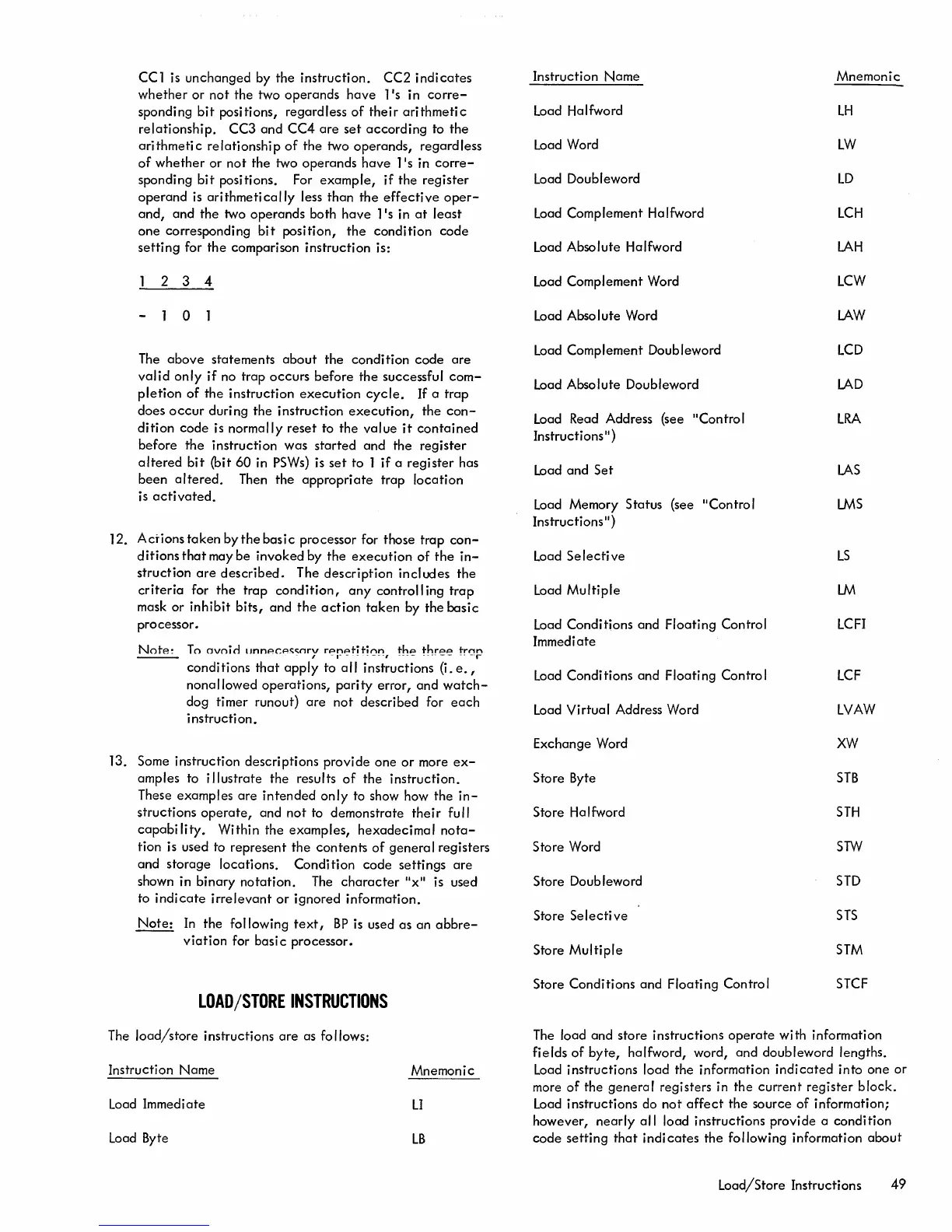

234

o

The

above

statements

about

the

condition

code

are

valid

only

if

no trap

occurs

before

the

successful

com-

pletion

of

the

instruction

execution

cycle.

If a

trap

does

occur

during

the

instruction

execution,

the

con-

dition

code

is normally

reset

to

the

value

it

contained

before

the

instruction was

started

and

the

register

altered

bit

(bit

60

in

PSWs)

is

set

to

1

if

a

register

has

been

altered.

Then

the

appropriate

trap

location

is

activated.

12.

Adionstakenbythebasic

processor for those

trap

con-

ditions

that

may

be

invoked by

the

execution

of

the

in-

struction

are

described.

The

description

includes

the

criteria

for

the

trap

condition,

any

control I ing

trap

mask

or

inhibit

bits,

and

the

action

taken

by

the

basic

processor.

Nnte~

Tn

avnin

IJnnpcpc;c;nrv

rpnptitinn

thp

thrpp

t

..

"n

~

,

-.---------,

----

-_.---

-'--r

conditions

that

apply

to

all

instructions (i.

e.,

nona"owed

operations,

parity

error, and

watch-

dog timer runout)

are

not

described

for

each

instruction.

13. Some instruction

descriptions

provide

one

or

more

ex-

amples to i

"ustrate

the

results

of

the

instruction.

These examples

are

intended

only

to show how

the

in-

structions

operate,

and

not

to demonstrate

their

full

capabi

lity. Within the

examples,

hexadecimal

nota-

tion is used to

represent

the

contents

of

general

registers

and

storage

locations.

Condition

code

settings

are

shown in

binary

notation.

The

character

"x"

is used

to

indicate

irrelevant

or

ignored

information.

Note:

In

the

following

text,

BP

is used

as

an

abbre-

viation

for basi c processor.

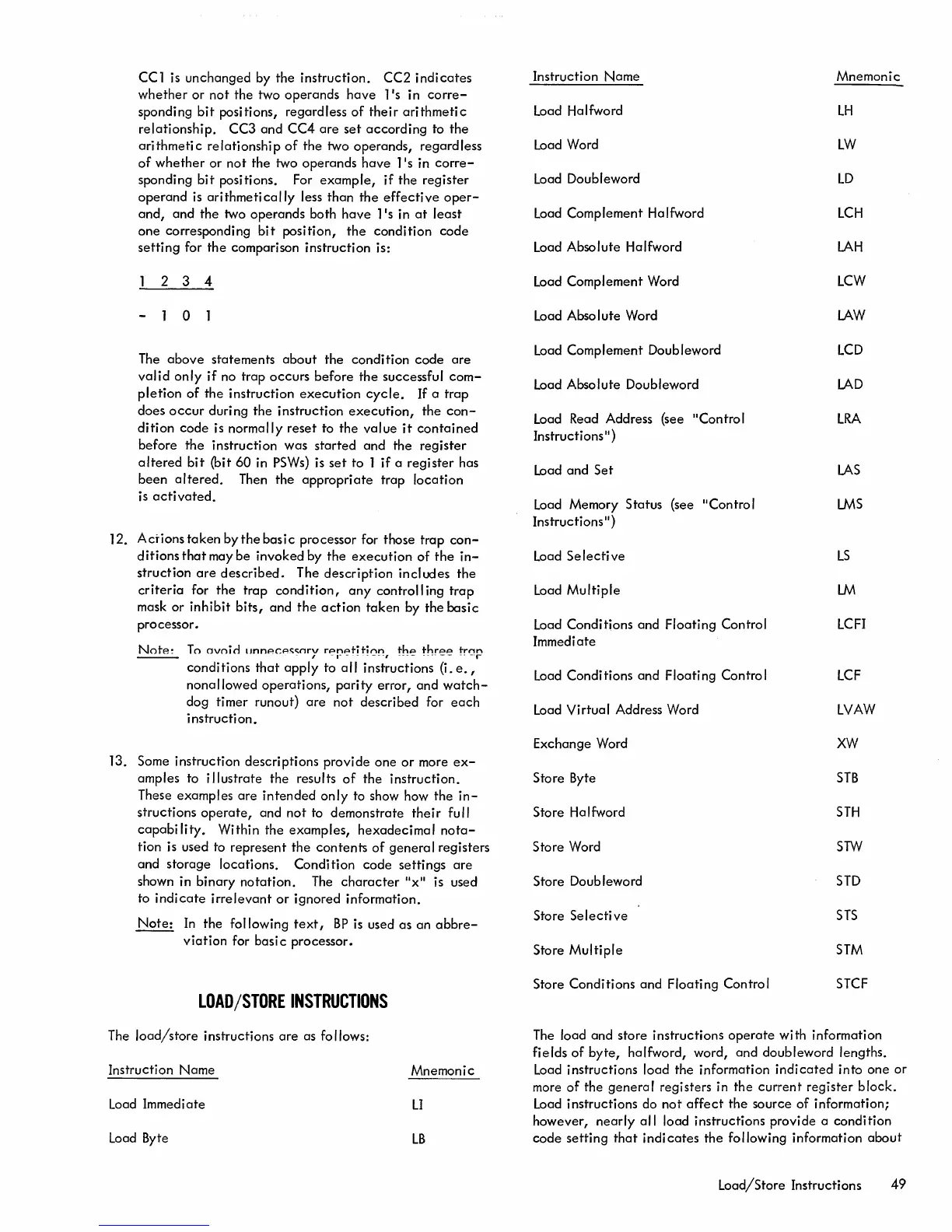

LOAD

jSTORE

INSTRUCTIONS

The

load/store

instructions

are

as follows:

Instruction

Name

Mnemonic

Load Immediate

LI

Load Byte

LB

Instruction

Name

Load Halfword

Load Word

Load Doubleword

Load

Complement Halfword

Load Absolute Halfword

Load

Complement Word

Load Absolute Word

Load

Complement Doubleword

Load Absolute Doubleword

Load Read Address (see

"Control

Instructions" )

Load

and

Set

Load Memory Status (see "Control

Instructions ")

Load

Selective

Load

Multiple

Load Conditions and Floating Control

Immediate

Load

Conditions and Floating Control

Load

Virtual

Address Word

Exchange Word

Store Byte

Store Halfword

Store Word

Store Doubleword

Store

Selective

Store

Multiple

Store Conditions

and

Floating Control

Mnemonic

LH

LW

LD

LCH

LAH

LCW

LAW

LCD

LAD

LRA

LAS

LMS

LS

LM

LCFI

LCF

LVAW

XW

STB

STH

STW

STD

STS

STM

STCF

The load and store instructions

operate

with information

fields

of

byte,

halfword, word, and doubleword lengths.

Load instructions load

the

information

indicated

into

one

or

more

of

the

general

registers in

the

current

register

block.

Load instructions do

not

affect

the

source

of

information;

however,

nearly

all

load instructions provide a

condition

code

setting

that

indicates

the

following information

about

Load/Store Instructions

49

Loading...

Loading...