Bit

Table

15.

Device Status Byte (Register R or

Ru

1)

(510,

no,

and HIO only)

(cont.)

Position

Significance

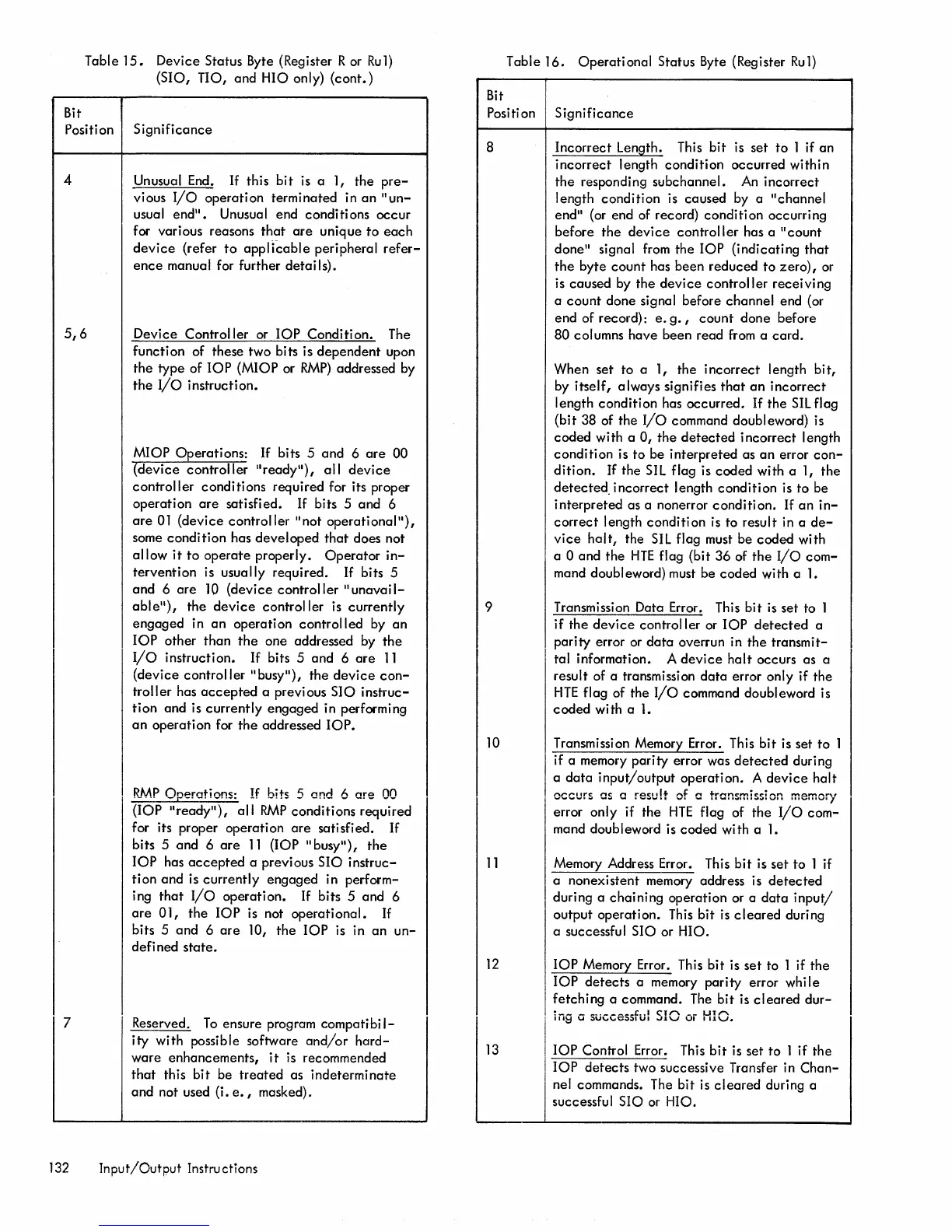

4

5,6

7

Unusual End.

If

this

bit

is a 1, the

pre-

vious

I/o

operation terminated in

an

"

un

-

usual

end".

Unusual end conditions

occur

for various reasons

that

are

unique

to

each

device

(refer

to

applicable

peripheral

refer-

ence

manual for further details).

Device Controller or

lOP

Condition. The

function of these two bits is

dependent

upon

the

type of

lOP

(MIOP or

RMP)

addressed by

the

I/o

instruction.

MIOP Operations:

If

bits 5

and

6

are

00

(device

controller

"ready"),

all

device

controller

conditions required for its proper

operation

are

satisfied.

If

bits 5 and 6

are

01

(device

controller

"not

operational"),

some

condition

has developed

that

does not

a II

ow

it

to

operate

properly.

Operator

i

n-

tervention is usually required. If bits 5

and

6

are

10

{device

controller

II

unavail-

able"},

the

device

controller

is

currently

engaged in

an

operation

controlled

by

an

lOP

other

than

the

one addressed by

the

I/O

instruction.

If

bits 5 and 6

are

11

(device

controller

II

busy"), the

device

con-

troller has

accepted

a previous 510 instruc-

tion and is

currently

engaged in performing

an

operation for

the

addressed

lOP.

RMP

Operations: If bits 5 and 6

are

00

(lOP

"ready"),

all

RMP

conditions required

for its proper operation

are

satisfied.

If

bits 5 and 6

are

11

(lOP

II

busy"),

the

lOP

has

accepted

a previous 510 instruc-

tion and is currently engaged in perform-

ing

that

I/o

operation.

If

bits 5 and 6

are

01,

the

lOP

is

not

operational.

If

bits 5 and 6

are

10,

the

lOP

is

in

an

un-

defi ned

state.

Reserved .

To

ensure program compati

bi

1-

ity

with possible software

and/or

hard-

ware enhancements,

it

is

recommended

that

this bit be

treated

as indeterminate

and

not used (i. e., masked).

132

Input/Output

Instru ctions

Table

16.

Operational Status Byte (Register

Ru1)

Bit

Position

Significance

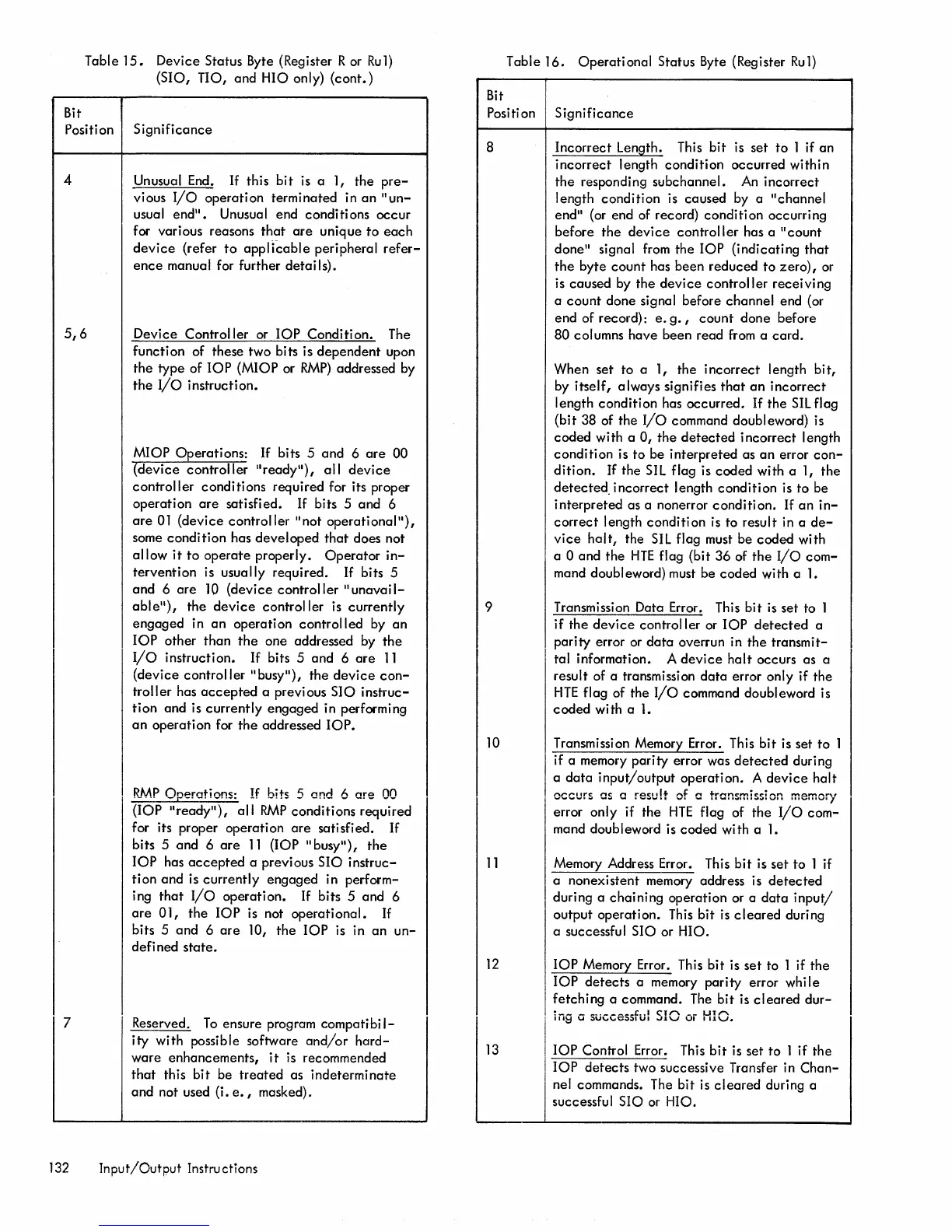

8

9

Incorrect Length. This bit is set

to

1 if

an

incorrect

length condition occurred within

the

responding subchannel.

An

incorrect

length condition is caused by a IIchannel

end" (or end of record)

condition

occurring

before

the

device

controller

has a

"count

done" signal from the

lOP

(indicating

that

the

byte

count

has been reduced

to

zero),

or

is caused by

the

device

controller

receiving

a

count

done signal before channel end (or

end of record):

e.

g.,

count

done before

80

columns have been read from a

card.

When set to a 1, the

incorrect

length

bit,

by itself, always signifies

that

an

incorrect

length condition has occurred.

If

the

SIL

flag

(bit

38 of the

I/o

command doubleword) is

coded

with a

0,

the

detected

incorrect length

condition

is to be interpreted as

an

error

con-

dition.

If the

SIL

flag is coded with a 1,

the

detected.

incorrect length condition is to be

interpreted as a nonerror

condition.

If

an

in-

correct

length condition is to result in a

de-

vice

halt,

the

SIL

flag must be

coded

with

a 0 and the

HTE

flag (bit

36

of

the

I/o

com-

mand doubl eword) must be coded

wi

th a

1.

Transmission Data Error. This bit

is

set to 1

if

the

device

controller or

lOP

detected

a

parity error or

data

overrun in

the

transmit-

tal information. A

device

halt

occurs as a

result of a transmission

data

error only if the

HTE

flag of the

I/o

command doubleword is

coded

with a

1.

10

Transmission Memory Error. This bit

is

set

to

1

if a memory parity error was

detected

during

a

data

input/output

operation. A

device

halt

11

occurs

as a result

of

a transm:ss:on memory

error only

if

the

HTE

flag of

the

I/O

com-

mand doubleword is coded with a

1.

Memory Address Error. This

bit

is set to 1 if

a nonexistent memory address is

detected

during a chaining operation or a

data

input/

output operation. This bit

is

cleared

during

a successful 510 or HIO.

12

lOP

Memory Error. This bit is

set

to 1 if

the

lOP

detects

a memory parity error while

fetching a command. The

bit

is

cleared

dur-

13

:

___

~

..

___

~~.c

..

1

C'l"

~_

WI'"'

,

III~

1.1

::IU\.o\.oC::I::IIUI

..JJ.V

UI

IIJ.V.

lOP

Control Error. This

bit

is set to 1 if the

lOP

detects

two successive Transfer in

Chan-

nel commands. The bit is

cleared

during a

successful

510 or HIO.

Loading...

Loading...