Zynq-7000 PCB Design Guide www.xilinx.com 17

UG933 (v1.8) November 7, 2014

Chapter 3: Power Distribution System

inches of the device’s outer edge is acceptable. The 0.47 µF capacitors should be placed as

close to the AP SoC as possible, within 0.5 inches of the outer edge.

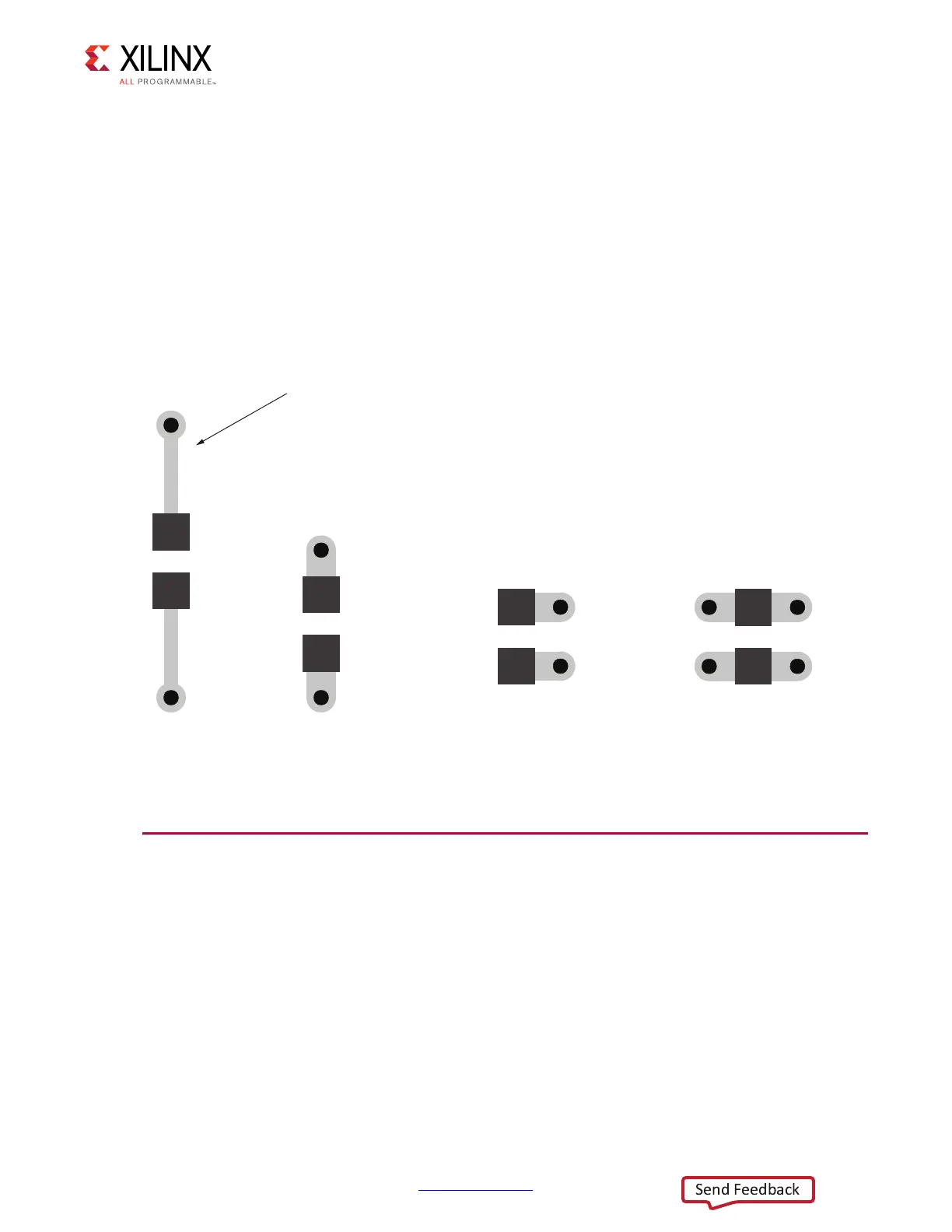

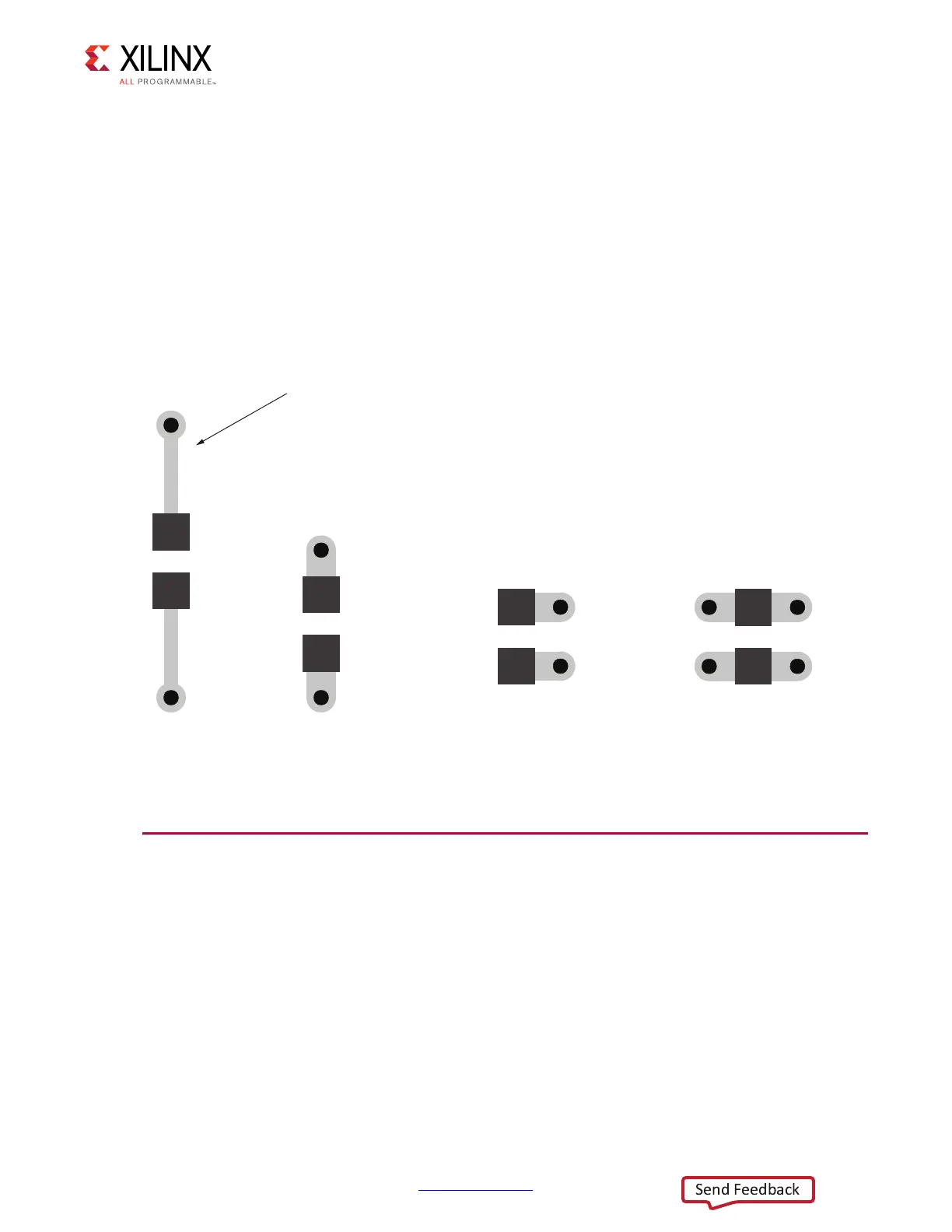

The capacitor mounting (solder lands, traces, and vias) should be optimized for low

inductance. Vias should be butted directly against the pads. Vias can be located at the ends

of the pads (see Figure 3-1B), but are more optimally located at the sides of the pads (see

Figure 3-1C). Via placement at the sides of the pads decreases the mounting’s overall

parasitic inductance by increasing the mutual inductive coupling of one via to the other.

Dual vias can be placed on both sides of the pads (see Figure 3-1D) for even lower parasitic

inductance, but with diminishing returns.

Basic PDS Principles

The purpose of the PDS and the properties of its components are discussed in this section.

The important aspects of capacitor placement, capacitor mounting, PCB geometry, and PCB

stackup recommendations are also described.

Noise Limits

In the same way that devices in a system have a requirement for the amount of current

consumed by the power system, there is also a requirement for the cleanliness of the power.

This cleanliness requirement specifies a maximum amount of noise present on the power

X-Ref Target - Figure 3-1

Figure 3-1: Example Capacitor Land and Mounting Geometries

Land Pattern

End Vias

Long Traces

(A)

UG933_c3_01_102413

(B)

Land Pattern

End Vias

Not Recommended.

Connecting Trace is Too Long

(C)

Land Pattern

Side Vias

(D)

Land Pattern

Double Side Vias

Loading...

Loading...