Zynq-7000 PCB Design Guide www.xilinx.com 60

UG933 (v1.8) November 7, 2014

Chapter 5: Processing System (PS) Power and Signaling

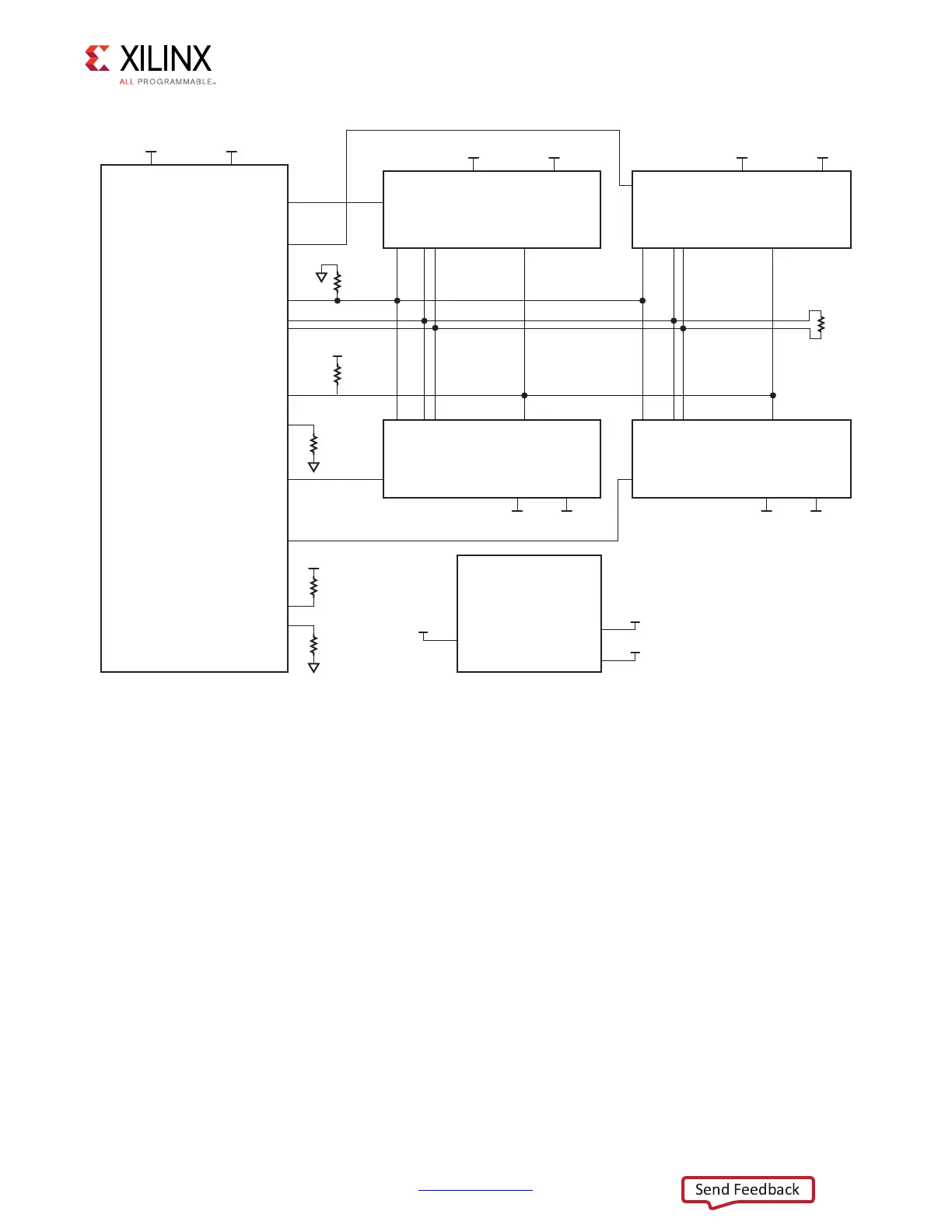

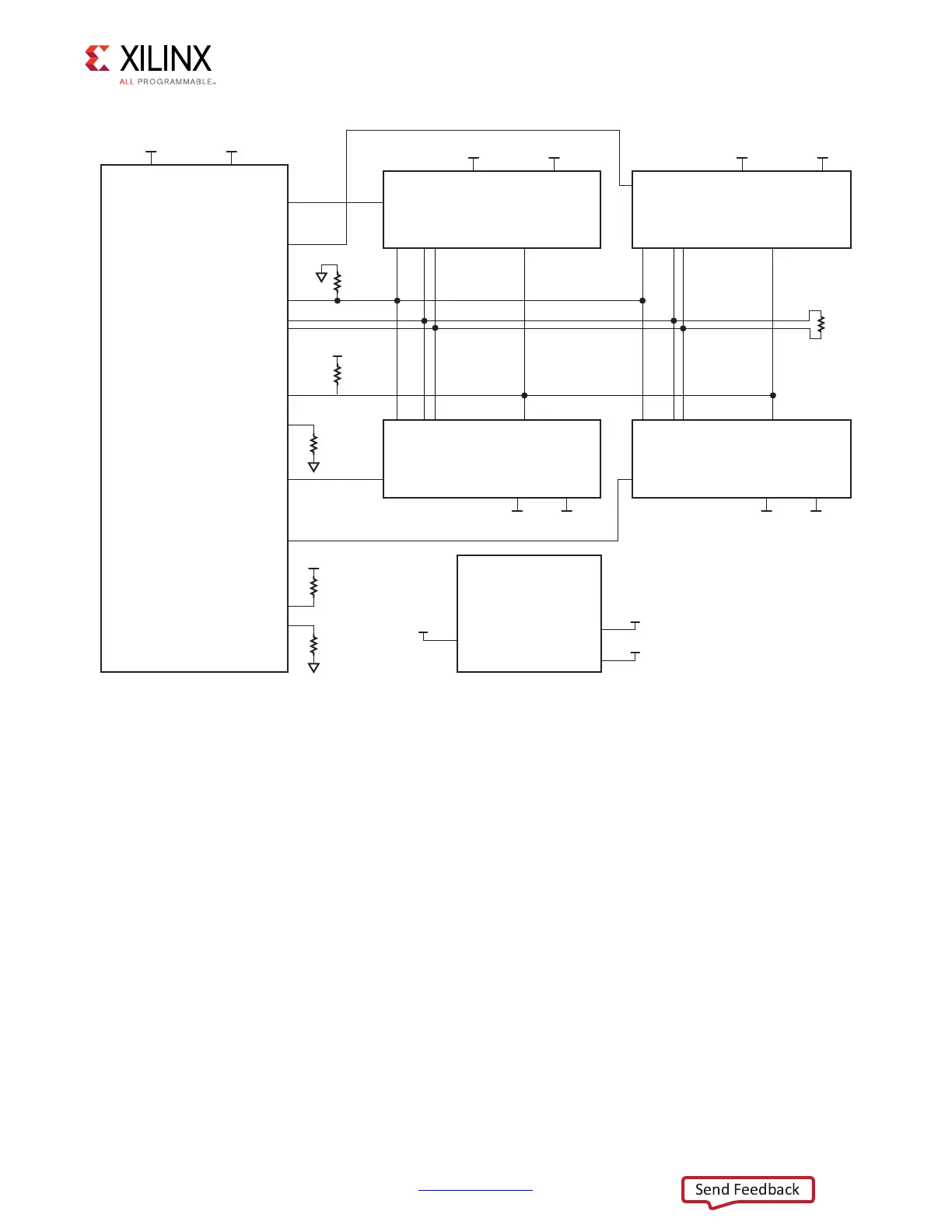

X-Ref Target - Figure 5-6

Figure 5-6: DDR2 Board Implementation

VREF VDDQ

VREF VDDQ

VREF VDDQ

VREF VDDQ

VREF VDDQ

VREF VDDQ

VREF VDDQ

VREF VDDQ

VREF

VTT

VREF

VTT

VDDQ

VDDQ

VDDQ

DDR

Termination

Regulator

VTT

Rterm

Rdown

VREF VDDQ

VREF VDDQ

Addr, Command, Contrl

(Addr, we_b, ras_b,

cas_b, cs_b)

Addr, Command, Contrl (Addr,

we_b, ras_b, cas_b, odt, cs_b)

Addr, Command, Contrl (Addr,

we_b, ras_b, cas_b, odt, cs_b)

cke

cke cke

cke

Addr, Command, Contrl (Addr,

we_b, ras_b, cas_b, odt, cs_b)

Addr, Command, Contrl (Addr,

we_b, ras_b, cas_b, odt, cs_b)

CLK_P

CLK_N

Cke

VRN

VRP

Data Group 0

(dq, dqs, dm)

Data Group 1

(dq, dqs, dm)

Data Group 2

(dq, dqs, dm)

Data Group

(dq, dqs, dm)

Data Group

(dq, dqs, dm)

Data Group

(dq, dqs, dm)

Data Group

(dq, dqs, dm)

UG933_c5_05_020614

Data Group 3

(dq, dqs, dm)

Rvrnp

Rvrnp

ZYNQ

DDR2 DDR2

DDR2 DDR2

Rclk

CLK

_P_N

CLK

_P_N

Rdown

ODT

CLK

_P_N

CLK

_P_N

Loading...

Loading...