Zynq-7000 PCB Design Guide www.xilinx.com 46

UG933 (v1.8) November 7, 2014

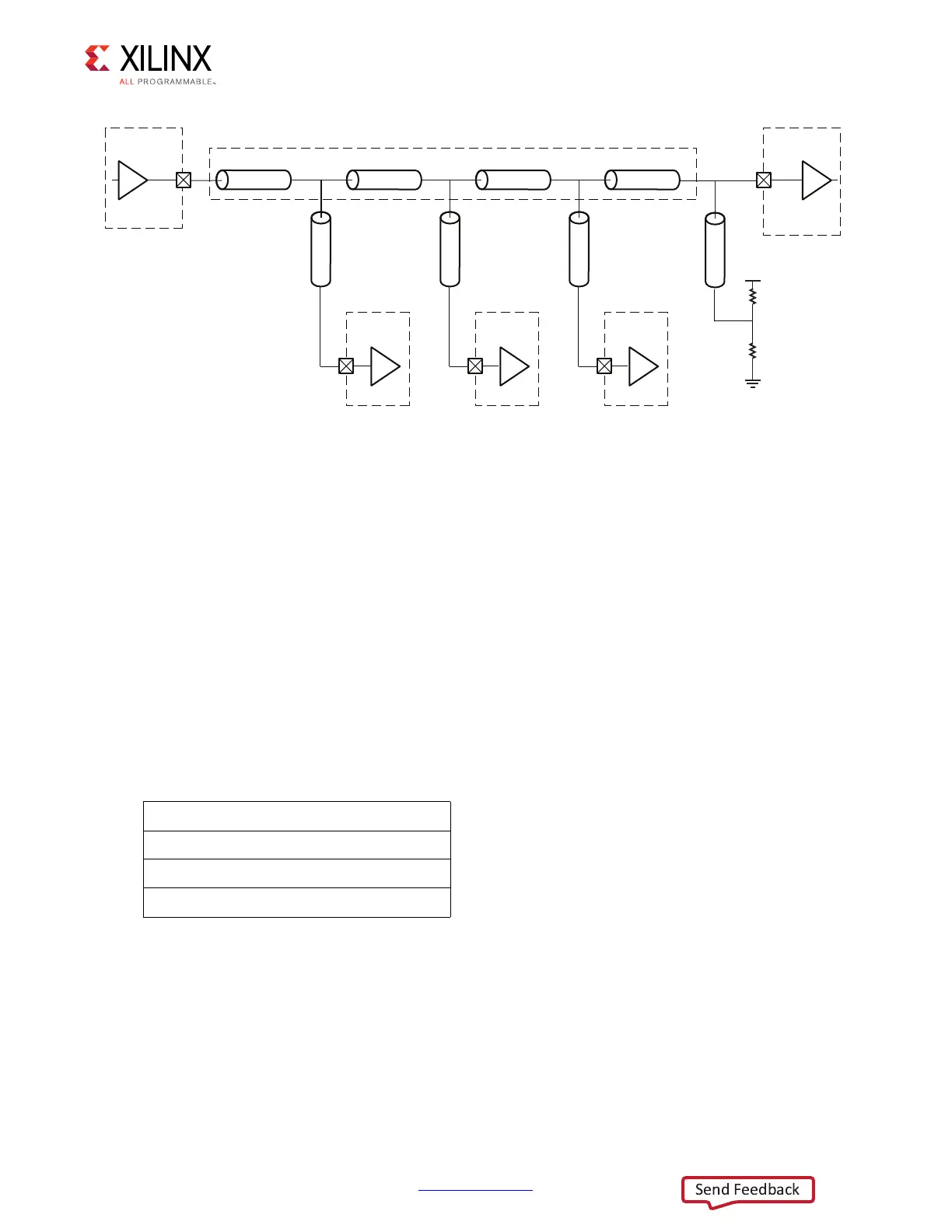

Chapter 4: SelectIO Signaling

The main transmission line should be kept as short as possible. Lengths up to 20 inches or

more are practical for most I/O standards as long as precise trace impedance is maintained

and crosstalk sources are avoided. The lengths of interim segments of the main

transmission line need not be equal. Their relative lengths can be arbitrary. Receivers at

different points along the main transmission line receive the signal with varying amounts of

delay, but all signal rise times are similar.

Stubs stretching from the main transmission line to the individual receivers must be kept as

short as possible. The longer these stubs become, the more corrupted the received

waveforms are. Simulation and measurement are required to assess signal integrity at the

individual receivers.

Table 4-2 lists example I/O interface types that can be used with the unidirectional

multi-drop topography.

LVTTL and LVCMOS do not specify any canonical termination method. Parallel termination

at the end of the long t-line is an appropriate termination method.

Bidirectional Topography and Termination

The two basic subsets of bidirectional topographies are point-to-point and multi-point. A

point-to-point topography has two transceivers (driver and receiver sharing one device

pin), while a multi-point topography can have many transceivers. Whether or not a

X-Ref Target - Figure 4-6

Figure 4-6: Basic Multi-Drop Topography

Output

Main Transmission Line

Input 4

2 x Z

0

= 100Ω

2 x Z

0

= 100Ω

V

CCO

Input 2

length < 8mm

Z

0

= 50ΩZ

0

= 50ΩZ

0

= 50ΩZ

0

= 50Ω

Input 3

length < 8mm

Z

0

= 50Ω

Z

0

= 50Ω

Z

0

= 50Ω

Z

0

= 50Ω

Input 1

length < 8mm

UG933_c4_06_031711

Table 4-2: Example I/O Interface Types for Unidirectional Multi-Drop I/O Topographies

LVTTL

LVC MOS

HSTL

SSTL

Loading...

Loading...