Zynq-7000 PCB Design Guide www.xilinx.com 61

UG933 (v1.8) November 7, 2014

Chapter 5: Processing System (PS) Power and Signaling

DDR Supply Voltages

Table 5-6 lists the different supply, reference and termination voltages required for

LPDDR2/DDR2/DDR3 memory. These voltages are also required to power the DDR I/O bank,

reference, and termination voltages.

Note:

V

REF

should track the midpoint of the VDD supplied to the DRAM and ground via

low-impedance paths. This can be done with a resistive divider or by a regulator that tracks this

midpoint. If resistive dividers are used, a separate divider and high-frequency decoupling capacitor

is recommended for each IC. If a regulator is used, a low impedance plane or planelet is

recommended for distribution.

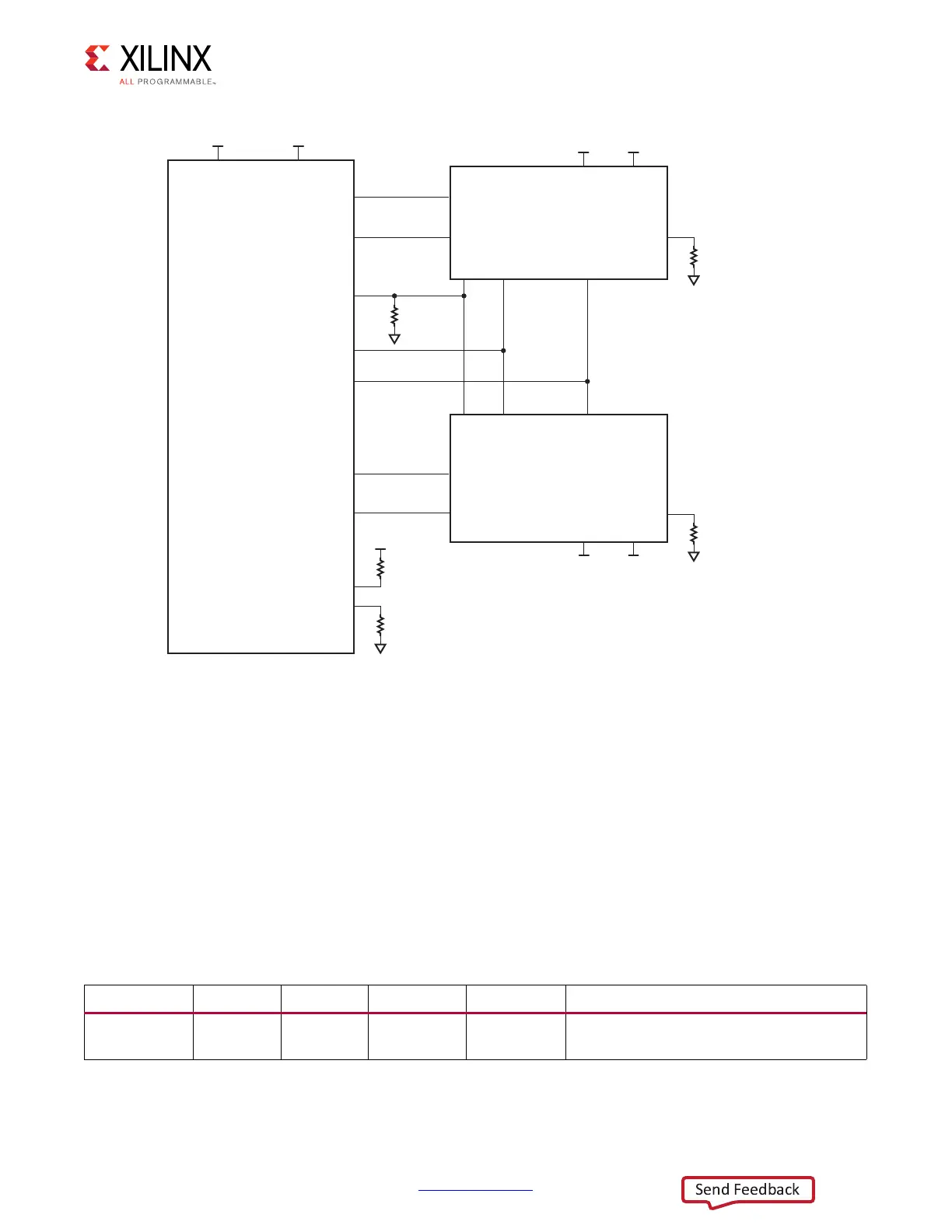

X-Ref Target - Figure 5-7

Figure 5-7: LPDDR2 Board Implementation

VREF VDDQ

VREF VDDQ

VREF VDDQ

VREF VDDQ

VDDQ

Rdown

VREF VDDQ

VREF VDDQ

Addr, Command, Contrl

(Addr, cs_b)

Addr, Command, Contrl

(CA, cs_b)

clkcke

clkcke

Addr, Command, Contrl

(CA, cs_b)

clk

Cke

VRN

VRP

Data Group 0

(dq, dqs, dm)

Data Group 1

(dq, dqs, dm)

Data Group 2

(dq, dqs, dm)

Data Group 0

(dq, dqs, dm)

Data Group 1

(dq, dqs, dm)

Data Group 0

(dq, dqs, dm)

Data Group 1

(dq, dqs, dm)

UG933_c5_06_102413

Data Group 3

(dq, dqs, dm)

Rvrnp

Rvrnp

zq

Rzq

zq

Rzq

ZYNQ

LPDDR2

LPDDR2

Table 5-6: DDR Voltage

Voltage LPDDR2 DDR2 DDR3 DDR3L Comments

V

CCO_DDR

V

DDQ

1.2V 1.8V 1.5V 1.35V

LPDDR2 devices also require V

DD1

(1.8V) and

V

DD2

(1.2V)

Loading...

Loading...