Zynq-7000 PCB Design Guide www.xilinx.com 62

UG933 (v1.8) November 7, 2014

Chapter 5: Processing System (PS) Power and Signaling

DDR Termination

For better signal integrity, DDR2 and DDR3 clock, address, command and control signals

need to be terminated. For DDR2, ODT and CKE are not terminated and should be pulled

down during memory initialization with a 4.7 kΩ resistor to GND. For DDR3, the DRST_B

signal is not terminated and should be pulled down during memory initialization with a

4.7 kΩ resistor to GND.

LPDDR2 does not require termination.

Table 5-7 shows the DDR termination requirements.

Note:

DDR3 memory also supports terminated DQS signals through the TDQS_P and TDQS_N pins.

This feature is not supported on Zynq-7000

AP SoC devices and those pins should be left floating.

DDR Trace Length

All DDR memory devices should be placed as closely to the Zynq-7000 AP SoC device as

possible. Tab l e 5-8 shows the maximum recommended trace lengths for DDR signals.

V

TT

V

DDQ

/2 V

DDQ

/2 V

DDQ

/2 V

DDQ

/2

Use a DDR termination regulator or a

resistor voltage divider to generate V

TT

and

V

REF

PS_DDR_V

REF0

PD_DDR_V

REF1

V

REF

V

DDQ

/2 V

DDQ

/2 V

DDQ

/2 V

DDQ

/2

Table 5-6: DDR Voltage (Cont’d)

Voltage LPDDR2 DDR2 DDR3 DDR3L Comments

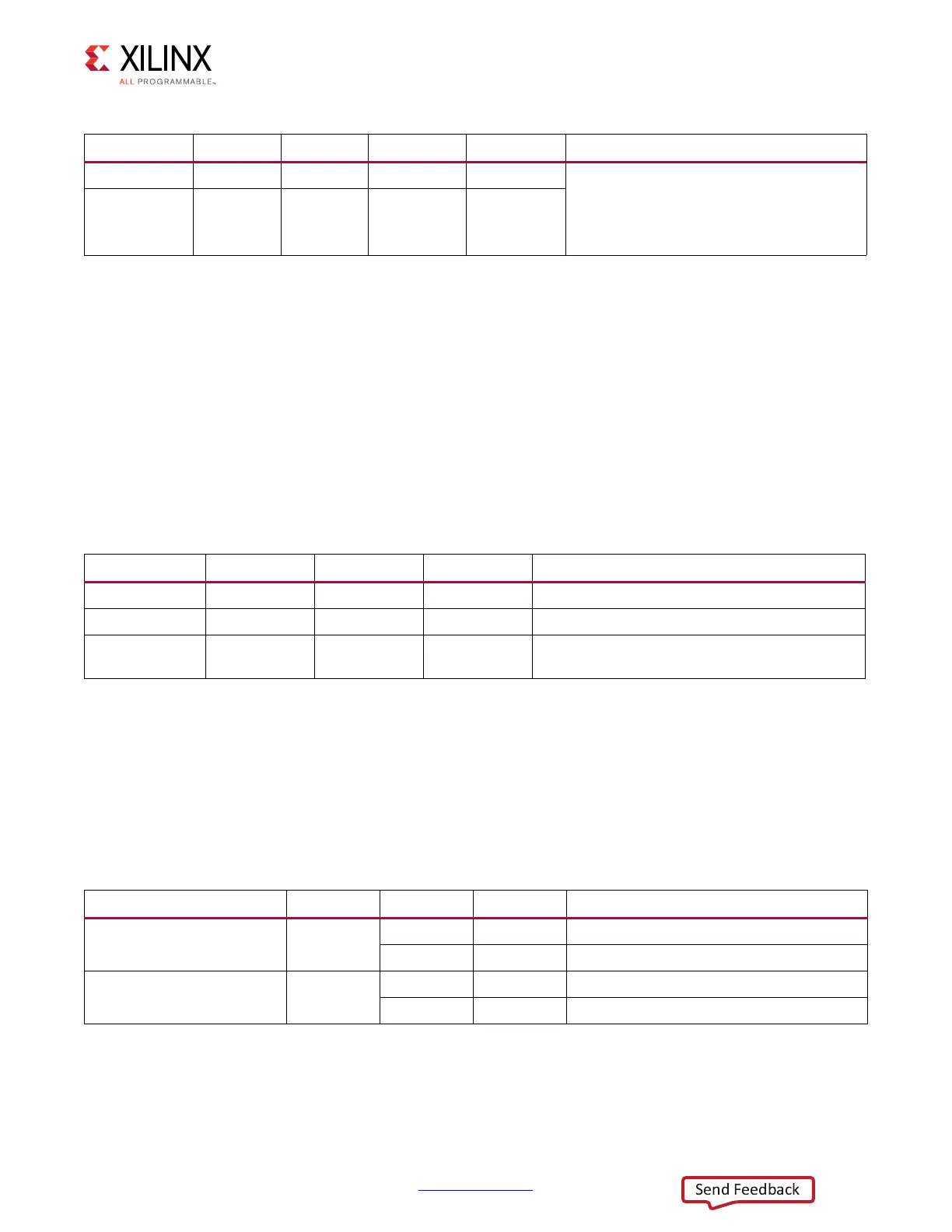

Table 5-7: DDR Termination

Termination LPDDR2 DDR2 DDR3/3L Comments

Rterm N/A 50Ω 40Ω

Rclk N/A 100Ω 80Ω

Rdown 4.7 KΩ 4.7 KΩ 4.7 KΩ

There is no DDR_DRST_B in LPDDR2/DDR2 device

side

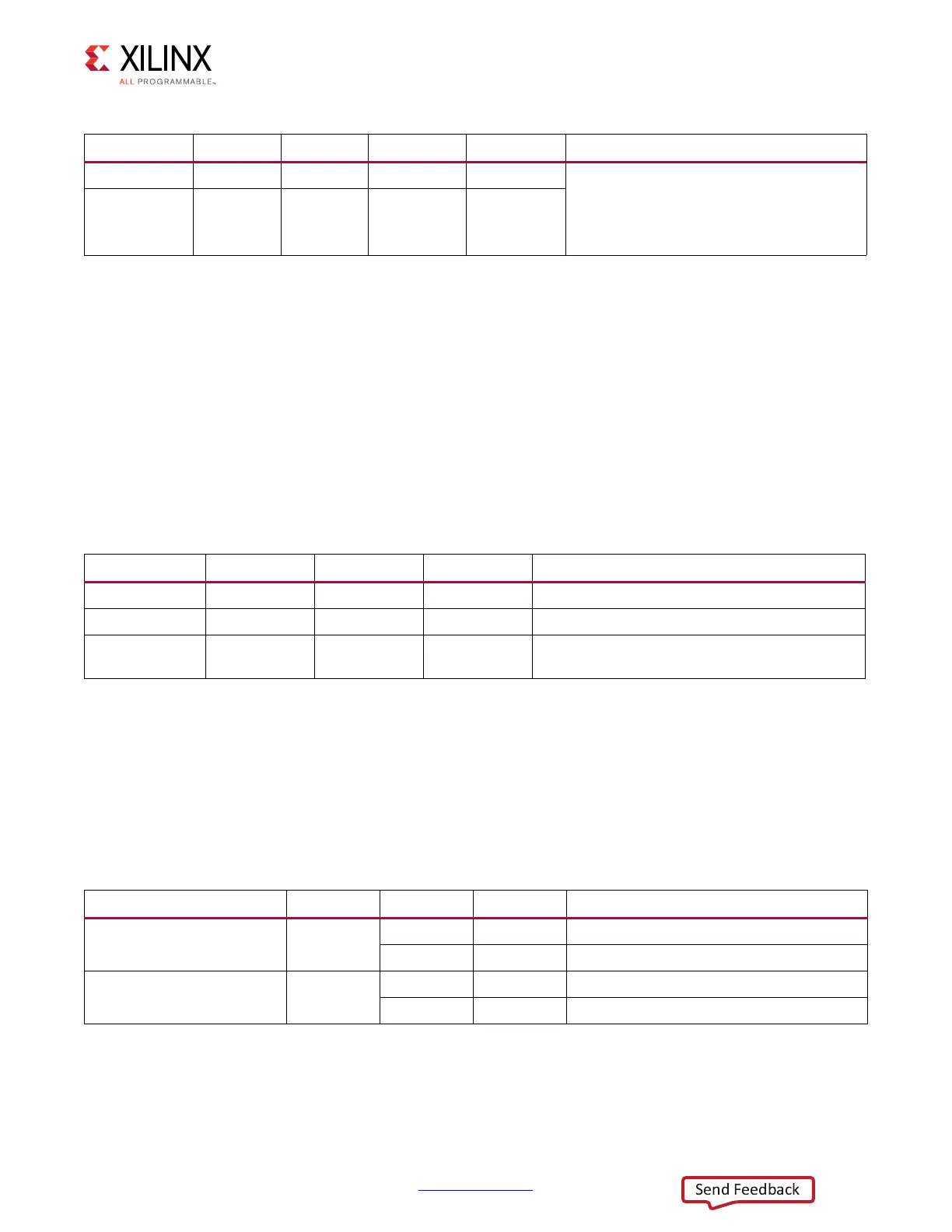

Table 5-8: DDR Max Trace Length

Signal Group LPDDR2 DDR2 DDR3/3L Comments

Data Group 1.5”

2” 2” Without guard-band

5” 5” With guard-band

(1)

Address, Command, Control 1.5”

3” 3” Without guard-band

5” 5” With guard-band

(1)

Notes:

1. A guard-band is a ring of copper driven by a low-impedance source to the same voltage as the high impedance node. It is

used to protect against surface leakage currents.

Loading...

Loading...