Zynq-7000 PCB Design Guide www.xilinx.com 23

UG933 (v1.8) November 7, 2014

Chapter 3: Power Distribution System

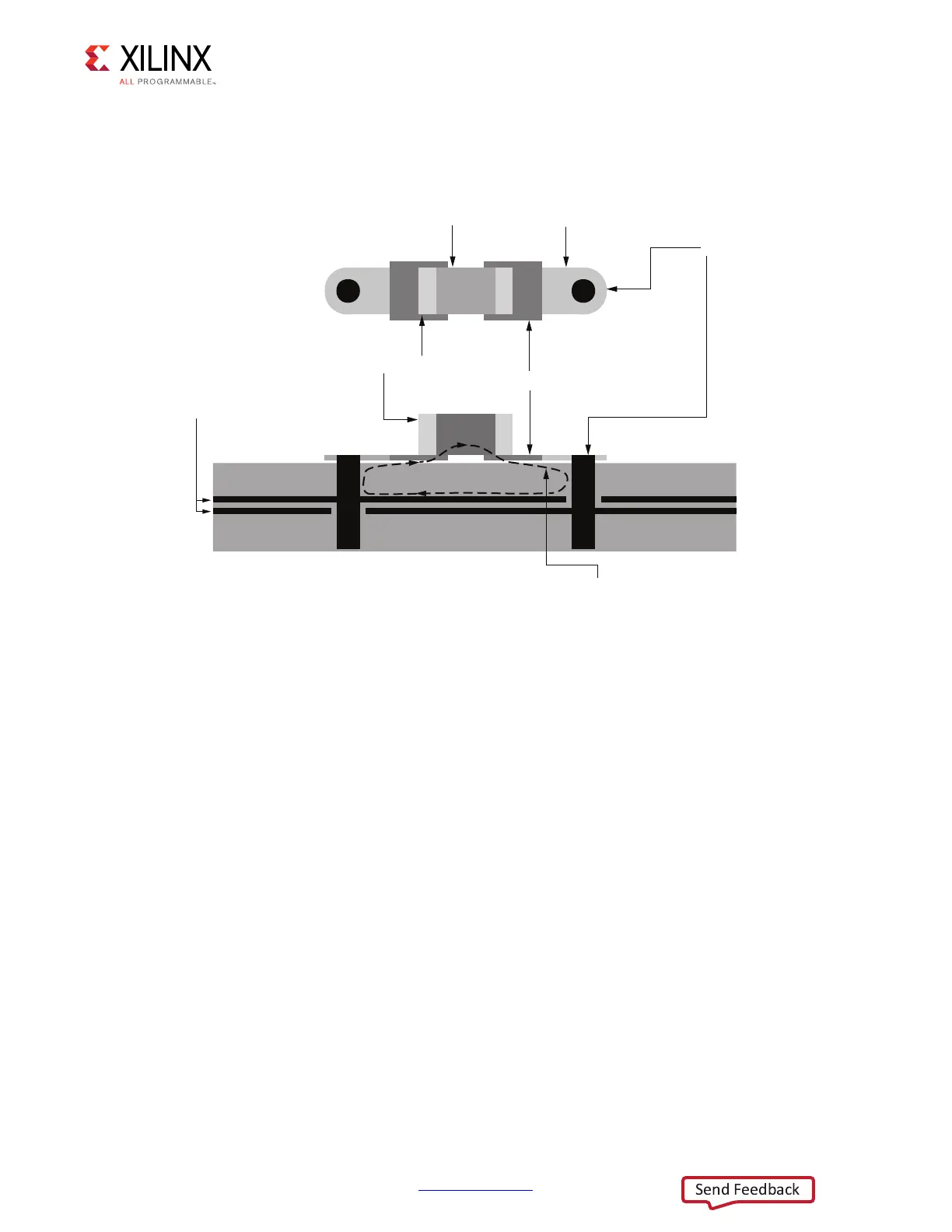

plane, up through one via, through the connecting trace to the land, through the capacitor,

through the other land and connecting trace, down through the other via, and into the

other plane, as shown in Figure 3-7.

A connecting trace length has a large impact on the mounting’s parasitic inductance and if

used, should be as short and wide as possible. When possible, a connecting trace should

not be used and the via should butt up against the land. Placing vias to the side of the

capacitor lands or doubling the number of vias, further reduces the mounting’s parasitic

inductance.

Some PCB manufacturing processes allow via-in-pad geometries, an option for reducing

parasitic inductance. Using multiple vias per land is important with ultra-low inductance

capacitors, such as reverse aspect ratio capacitors that place wide terminals on the sides of

the capacitor body instead of the ends.

PCB layout engineers often try to squeeze more parts into a small area by sharing vias

among multiple capacitors. This technique should not be used under any circumstances.

PDS improvement is very small when a second capacitor is connected to an existing

capacitor’s vias. For a larger improvement, reduce the total number of capacitors and

maintain a one-to-one ratio of lands to vias.

The capacitor mounting (lands, traces, and vias) typically contributes about the same

amount or more inductance than the capacitor's own parasitic self-inductance.

X-Ref Target - Figure 3-7

Figure 3-7: Example Cutaway View of PCB with Capacitor Mounting

Solderable End Terminal

0402 Capacitor Body

Surface Trace

Capacitor Solder Land

Via

PCB

GND

V

CC

Power and

Ground Planes

Mounted Capacitor Current Loop

UG933_c3_07_032811

Loading...

Loading...