MC96F6432

June 22, 2018 Ver. 2.9 115

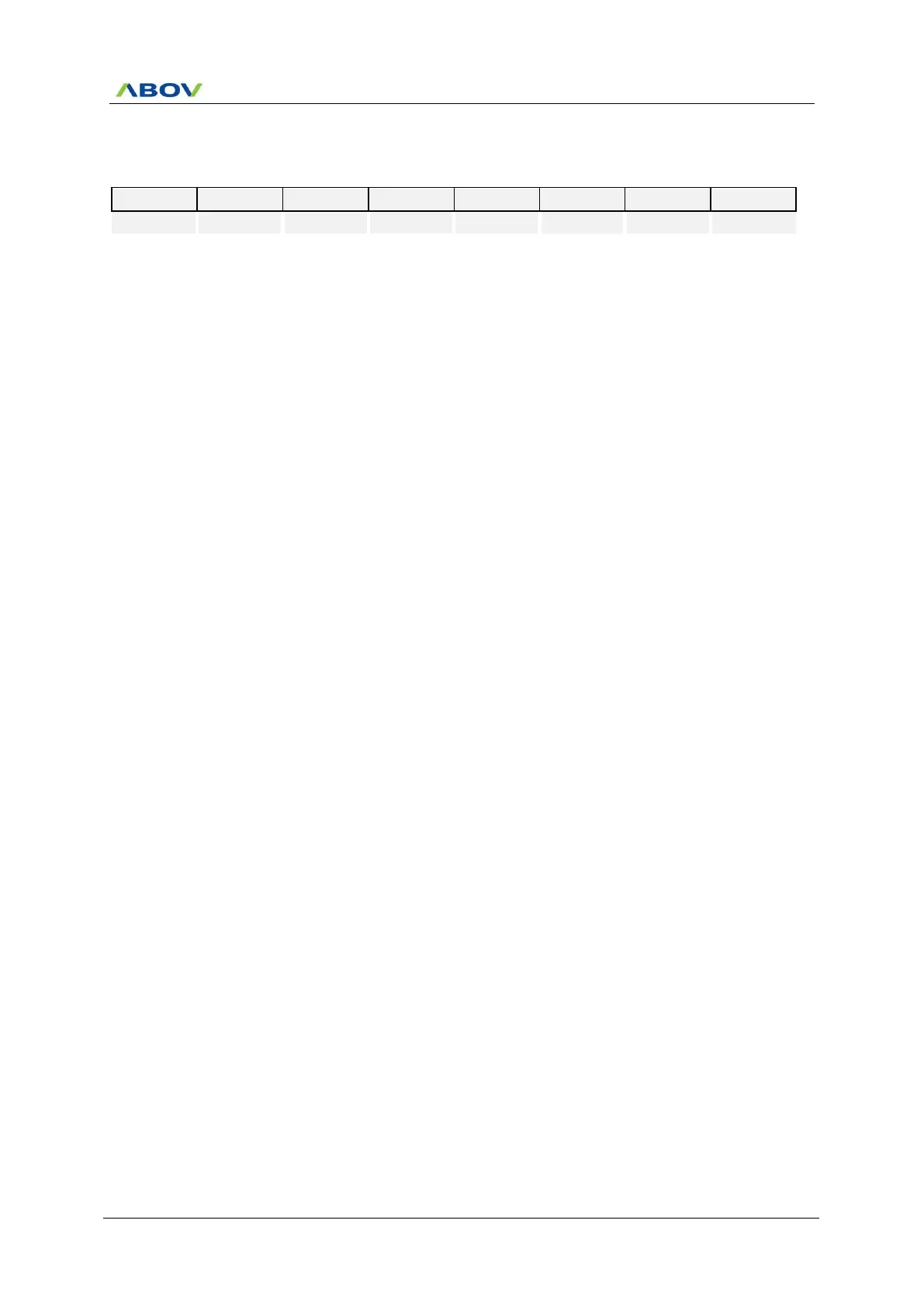

BITCR (Basic Interval Timer Control Register) : 8BH

Initial value : 01H

When BIT Interrupt occurs, this bit becomes ‘1’. For clearing bit, write ‘0’

to this bit or auto clear by INT_ACK signal. Writing “1” has no effect.

BIT interrupt no generation

If this bit is written to ‘1’, BIT Counter is cleared to ‘0’

Select BIT overflow period

Bit 0 overflow (BIT Clock * 2)

Bit 1 overflow (BIT Clock * 4) (default)

Bit 2 overflow (BIT Clock * 8)

Bit 3 overflow (BIT Clock * 16)

Bit 4 overflow (BIT Clock * 32)

Bit 5 overflow (BIT Clock * 64)

Bit 6 overflow (BIT Clock * 128)

Bit 7 overflow (BIT Clock * 256)

Loading...

Loading...