MC96F6432

188 June 22, 2018 Ver. 2.9

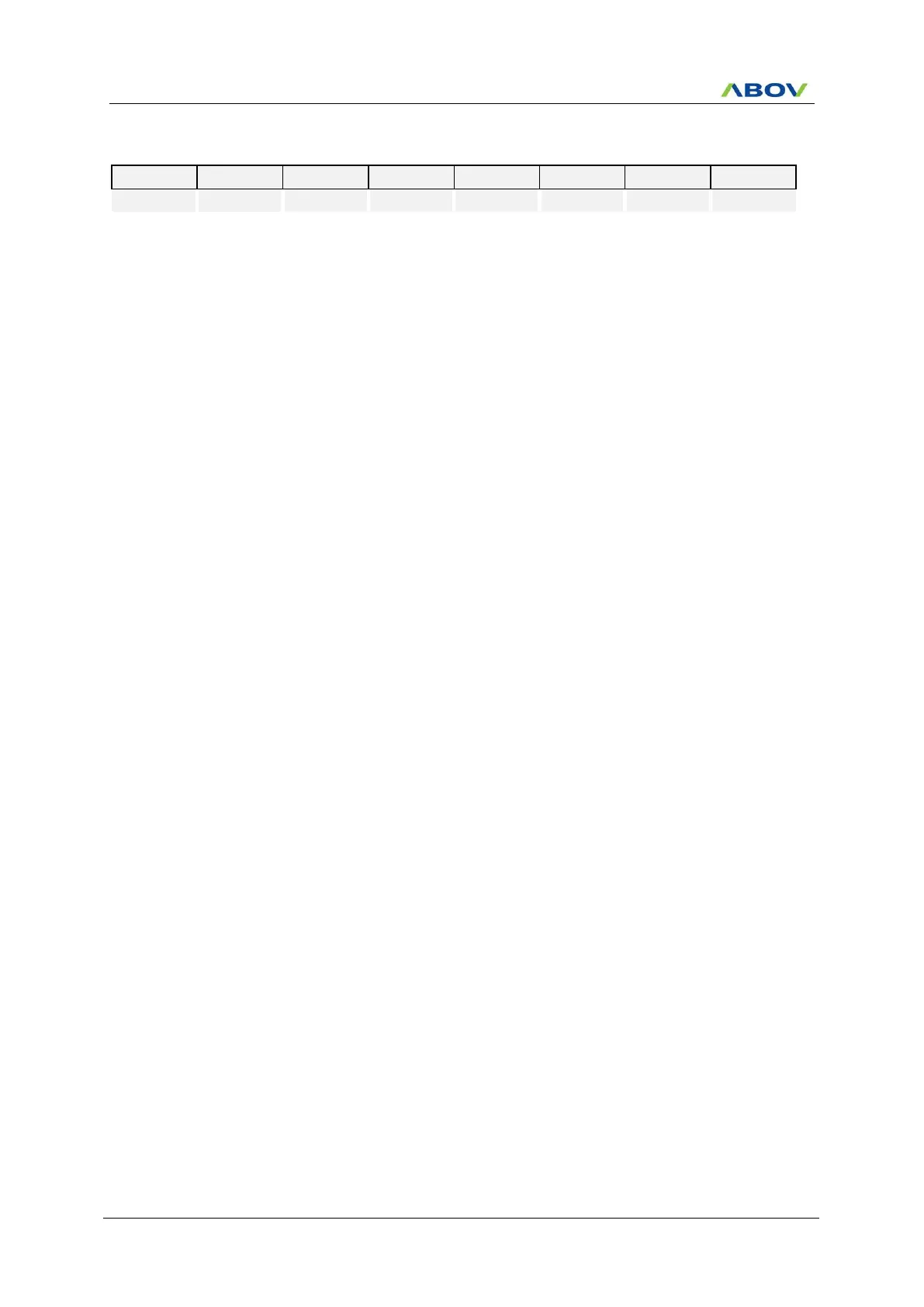

SPICR (SPI 2 Control Register) : B5H

Initial value : 00H

This bit controls the SPI 2 operation

This bit selects the data transmission sequence

This bit selects whether Master or Slave mode

This two bits control the serial clock (SCK2) mode.

Clock polarity(CPOL) bit determine SCK2’s value at idle mode.

Clcok phase (CPHA) bit determine if data are sampled on the leading or

trailing edge of SCK2.

These three bits select the SCK2 rate of the device configured as a

master. When DSCR bit is written one, SCK2 will be doubled in master

mode.

Loading...

Loading...