AD9361 Reference Manual UG-570

| Page 113 of 128

SERIAL PERIPHERAL INTERFACE (SPI)

The SPI bus provides the mechanism for all digital control of

the AD9361. Each SPI register is 8-bit wide, and each register

contains control bits, status monitors, or other settings that

control all functions of the device. The following sections

explain the specifics of this interface.

SPI Functional Layer

The SPI bus can be configured by setting the bit values in the

SPI Configuration register. This register is symmetrical; that is,

D6 is equivalent to D1, and D5 is equivalent to D2 (D4 and D3

are unused). The device powers up in its default mode (MSB-

first addressing), but can accept an LSB-first write to the SPI

Configuration register because of this symmetry. The

symmetrical bits are OR’ed together, so setting one bit sets both

in the pair. The bit order is MSB-first when D5 and D2 are left

clear, while bit order is swapped to LSB-first when these bits are

set. Once properly configured, all subsequent register writes

must follow the selected format.

The bus is configured as a 4-wire interface by default. If Bit D6

and Bit D1are set, the SPI bus is configured as a 3-wire

interface. Bit D7 and Bit D0 asynchronously reset all registers to

their default values when set, and these bits must be cleared

before other registers can be changed.

Each SPI bus signal is described in the following sections.

SPI_ENB

SPI_ENB is the bus enable signal driven from the BBP to the

AD9361. SPI_ENB is driven low before the first SPI_CLK rising

edge and is normally driven high again after the last SPI_CLK

falling edge. The AD9361 ignores the clock and data signals

while SPI_ENB is high. If the AD9361 is the only device on the

SPI bus, SPI_ENB can be tied low.

The SPI_DO and SPI_DI pins transition to a high impedance

state when this input is high. If driven high during any

communications cycle, that cycle is suspended until SPI_ENB

is reactivated low.

SPI_CLK

SPI_CLK is the interface reference clock driven by the BBP to

the AD9361. It is only active while SPI_ENB is low. The

maximum SPI_CLK frequency is 50 MHz.

SPI_DI, SPI_DO and SPI_DIO

When configured as a 4-wire bus, the SPI utilizes two data

signals: SPI_DI and SPI_DO. SPI_DI is the data input line

driven from the BBP to the AD9361 and SPI_DO is the data

output from the AD9361 to the BBP in this configuration.

When configured as a 3-wire bus, SP_DI is used as a

bidirectional data signal that both receives and transmits serial

data. In 3-wire configuration, this signal is referred to as

SP_DIO in this section to distinguish between the two

configurations.

The data signals are launched on the rising edge of SPI_CLK

and sampled on the falling edge of SPI_CLK by both the BBP

and the AD9361. SPI_DI (or SPI_DIO) carries the control field

from BBP to the AD9361 during all transactions and the write

data fields during a write transaction. SPI_DO (or SPI_DIO)

carries the returning read data fields from the AD9361 to BBP

during a read transaction.

The AD9361 does not provide any weak pull-ups or pull-downs

on these pins. When SPI_DO is inactive, it is floated in a high

impedance state. If a valid logic state on SPI_DO is required at

all times, an external weak pull-up/pull-down should be added

on the PCB.

SPI Data Transfer Protocol

The AD9361 SPI is a flexible, synchronous serial communica-

tions bus allowing seamless interfacing to many industry

standard microcontrollers and microprocessors. The serial I/O

is compatible with most synchronous transfer formats,

including both the Motorola SPI and Intel® SSR protocols. The

control field width for the AD9361 is limited to 16-bit only, and

multibyte IO operation is allowed. The AD9361 cannot be used

to control other devices on the bus—it only operates as a slave.

There are two phases to a communication cycle. Phase 1 is the

control cycle, which is the writing of a control word into the

AD9361. The control word provides the AD9361 serial port

controller with information regarding the data field transfer

cycle, which is Phase 2 of the communication cycle. The Phase 1

control field defines whether the upcoming data transfer is read

or write. It also defines the register address being accessed.

Phase 1 Instruction Format

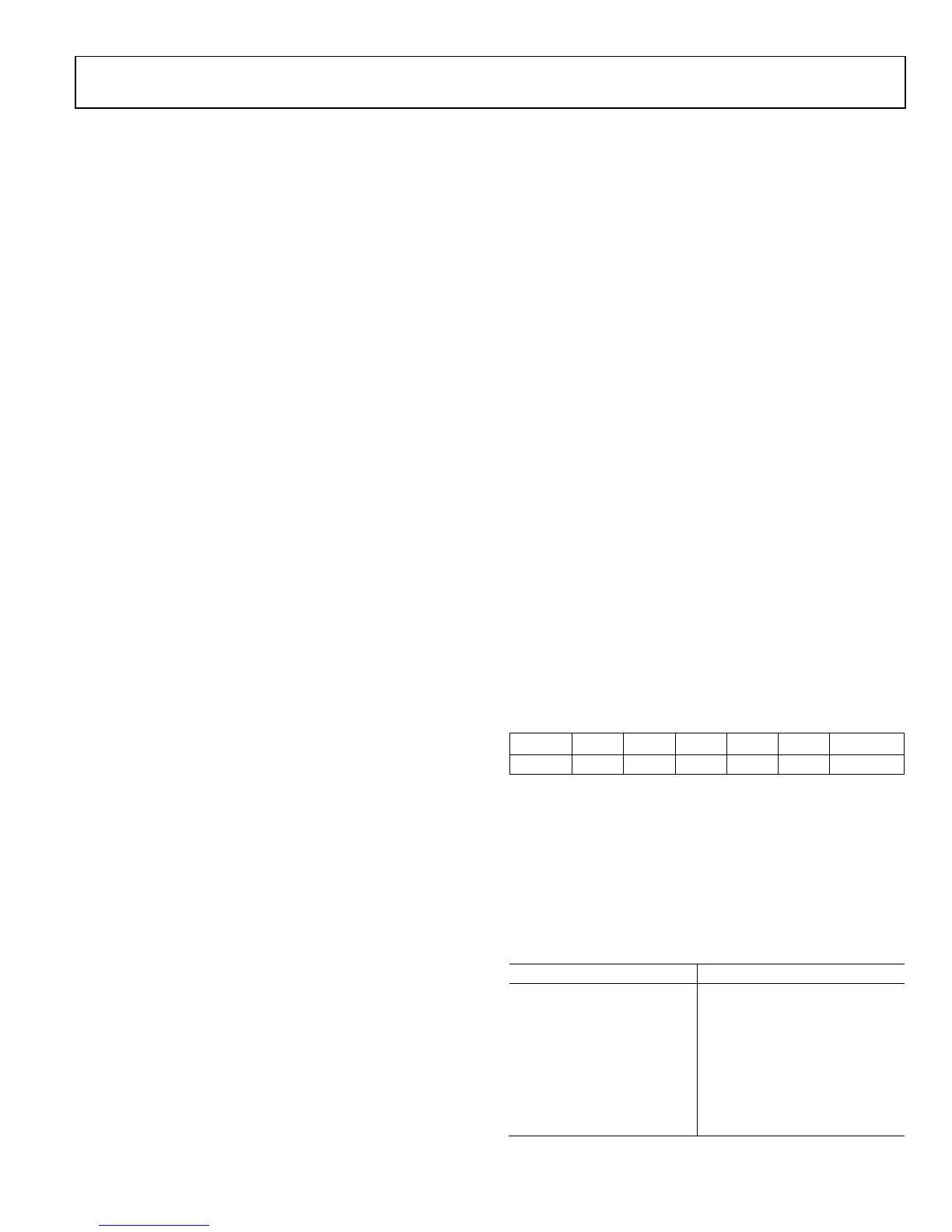

The 16-bit control field contains the following information:

MSB D14 D13 D12 D11 D10 D9:D0

W/Rb NB2 NB1 NB0 X X A[9:0]

W/Rb—Bit 15 of the instruction word determines whether a

read or write data transfer occurs after the instruction byte

write. Logic high indicates a write operation; logic zero

indicates a read operation.

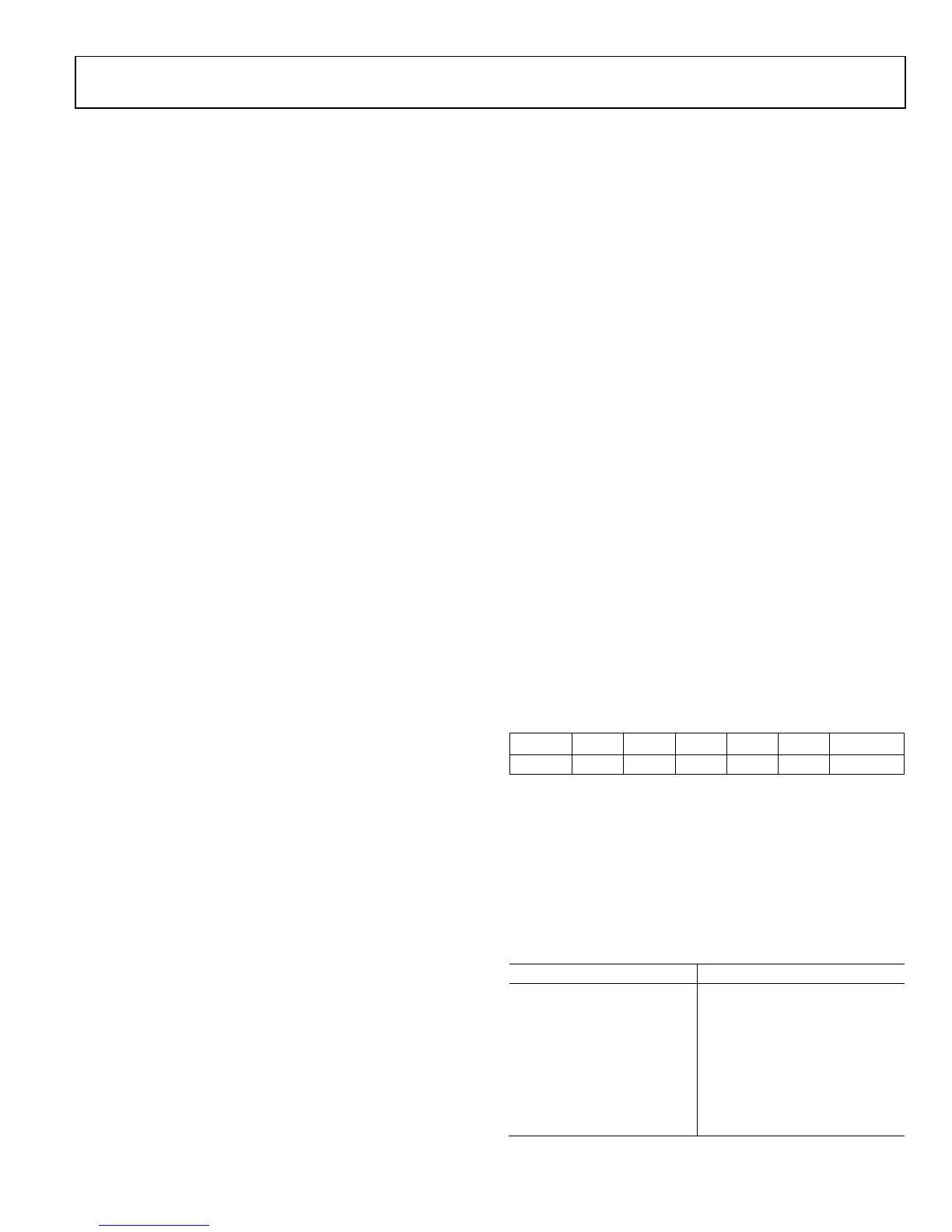

NB2, NB1, NB0—Bits [14:12] of the instruction word specify

the number of bytes transferred during Phase 2 of the IO

operation. Table 52 details the number of bytes transferred

during Phase 2 for each NB[2:0] combination.

Table 52.

NB2, NB1, NB0 Description

000 Transfer 1 byte

001 Transfer 2 bytes

010 Transfer 3 bytes

011 Transfer 4 bytes

100 Transfer 5 bytes

101 Transfer 6 bytes

110 Transfer 7 bytes

111 Transfer 8 bytes

Loading...

Loading...