AD9361 Reference Manual UG-570

| Page 23 of 128

CONFIGURING AND USING A FAST LOCK PROFILE

The Fast Lock registers (Address 0x25C through Address 0x25F for Rx, Address 0x29C through Address 0x29F for Tx) allow access to the

internal memory area. Refer to Table 11 for Rx and Table 12 for Tx fast lock register contents. The following procedure describes how to

define a particular profile to the currently programmed synthesizer frequency:

1. If using faster lock (wide BW), determine fast lock delay and N. If not using wide BW, then delay is not important and N = 1.

2. To configure profiles:

a. For each profile (Rx and Tx are independent),

i. Calibrate the synthesizer to the desired frequency using FDD calibration settings

ii. Create the profile and store in the AD9361 using the ad9361_fastlock_store function.

iii. If the profile also needs to be stored in the BBP then use the ad9361_fastlock_save function.

3. To use profiles:

a. To use a profile that is stored inside the AD9361 use the ad9361_fastlock_recall function.

b. If the profile is stored in the BBP then first load it into the AD9361 by using the ad9361_fastlock_load function, and then

use the recall function to use the profile.

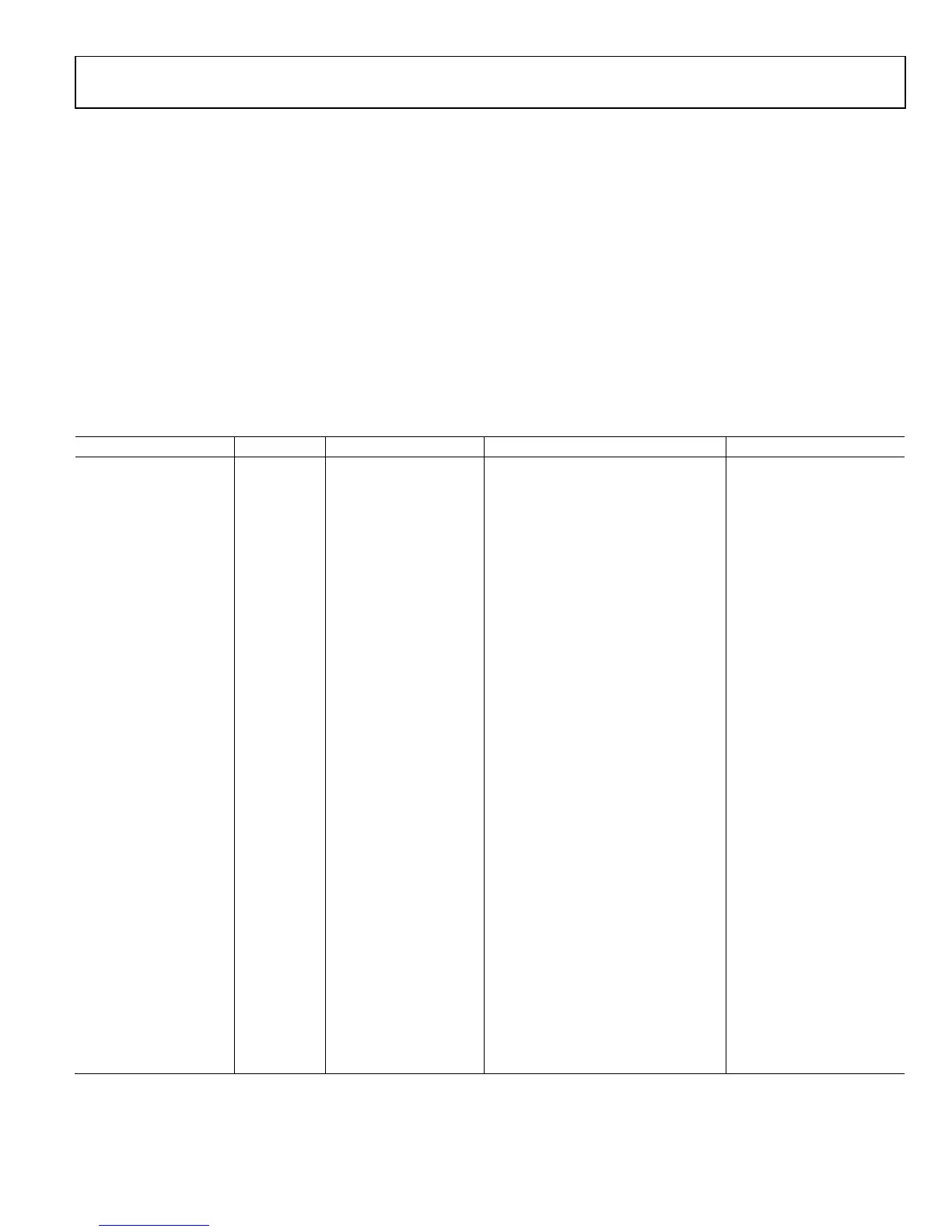

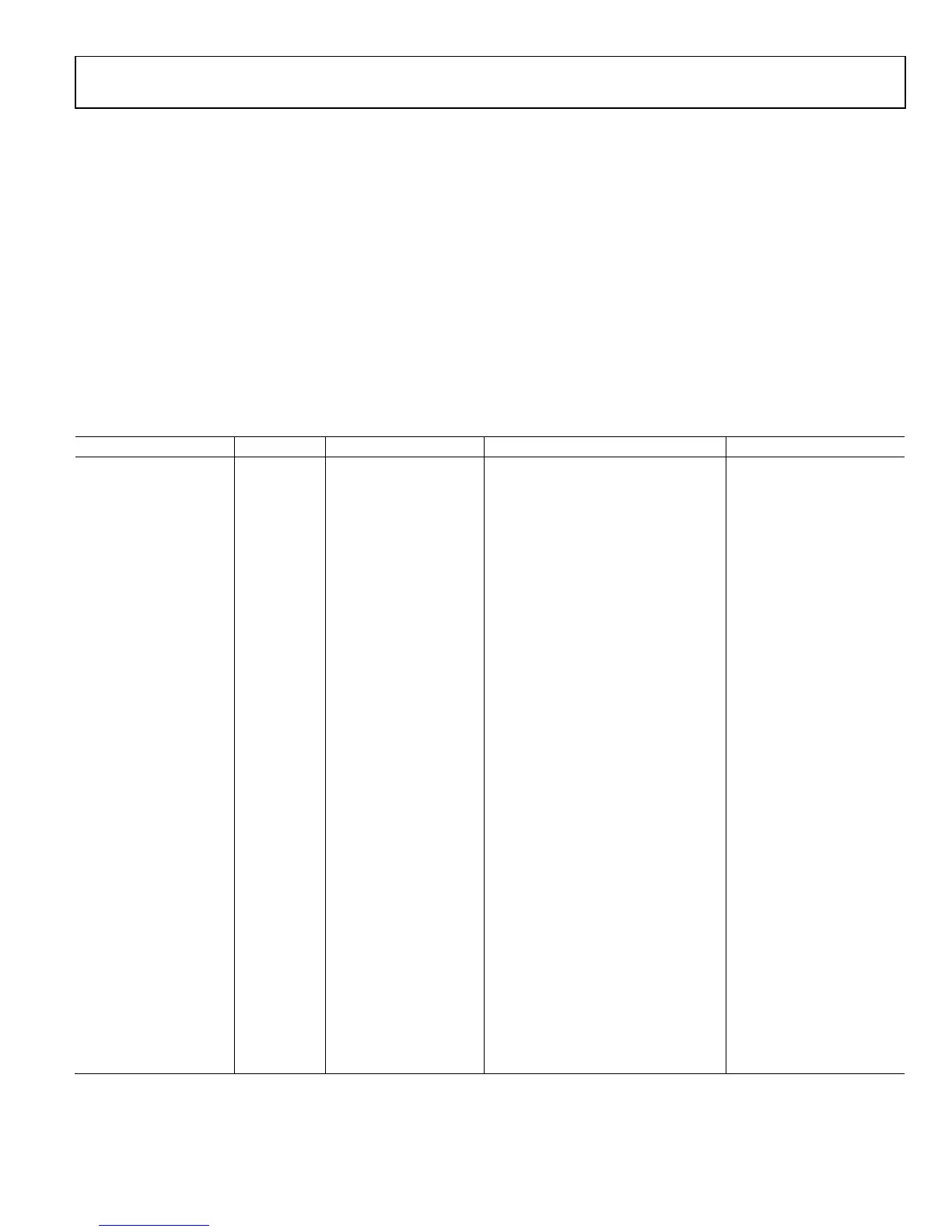

Table 11. Rx Fast Lock Internal Addressing

Program Address[7:4] Assignment Program Address[3:0] Assignment (Written to 0x25D) Location of Setup Words

0 profile0 0 Synthesizer Integer Word[7:0] 0x231[D7:D0]

1 profile1 1 Synthesizer Integer Word[10:8] 0x232[D2:D0]

2 profile2 2 Synthesizer Fractional Word[7:0] 0x233[D7:D0]

3 profile3 3 Synthesizer Fractional Word [15:8] 0x234[D7:D0]

4 profile4 4 Synthesizer Fractional Word [22:16] 0x235[D6:D0]

5 profile5 5 VCO Bias Ref[2:0] shift left by 4

+

VCO Varactor [3:0]

0x242[D2:D0]

0x239[D3:D0]

6 profile6 6 VCO Bias Tcf[1:0] shift left by 3

+

Charge Pump Current (Init)[5:0]

0x242[D4:D3]

Set per Init N calculation

7 profile7 7 Charge Pump Current[5:0] 0x23B[D5:D0]

8 Not used 8 Loop Filter R3[3:0] shift left by 4

+

Loop Filter R3 (Init)[3:0]

0x240[D3:D0]

Set desired Init value

9 Not used 9 Loop Filter C3[3:0] shift left by 4

+

Loop Filter C3 (Init)[3:0]

0x23F[D3:D0]

Set desired Init value

A Not used A Loop Filter C1[3:0] shift left by 4

+

Loop Filter C2[3:0] shift right by 4

0x23E[D3:D0]

0x23E[D7:D4])

B Not used B Loop Filter R1[3:0]

+

Loop Filter R1 (Init)[3:0]

0x23F[D7:D4]

Set per Init N calculation

C Not used C VCO Varactor Reference Tcf[2:0]

+

Rx VCO Divider[3:0]

0x250[D6:D4]

0x005[D3:D0]

D Not used D VCO Cal Offset[3:0] shift left by 1

+

VCO Varactor Reference[3:0]

0x238[D6:D3]

0x251[D3:D0]

E Not used E Force VCO Tune[7:0] 0x237[D7:D0]

F Not used F Force ALC word[6:0] shift left by 1

+

Force VCO Tune[8]

0x236[D6:D0]

0x238[D0]

Loading...

Loading...