UG-570 AD9361 Reference Manual

| Page 28 of 128

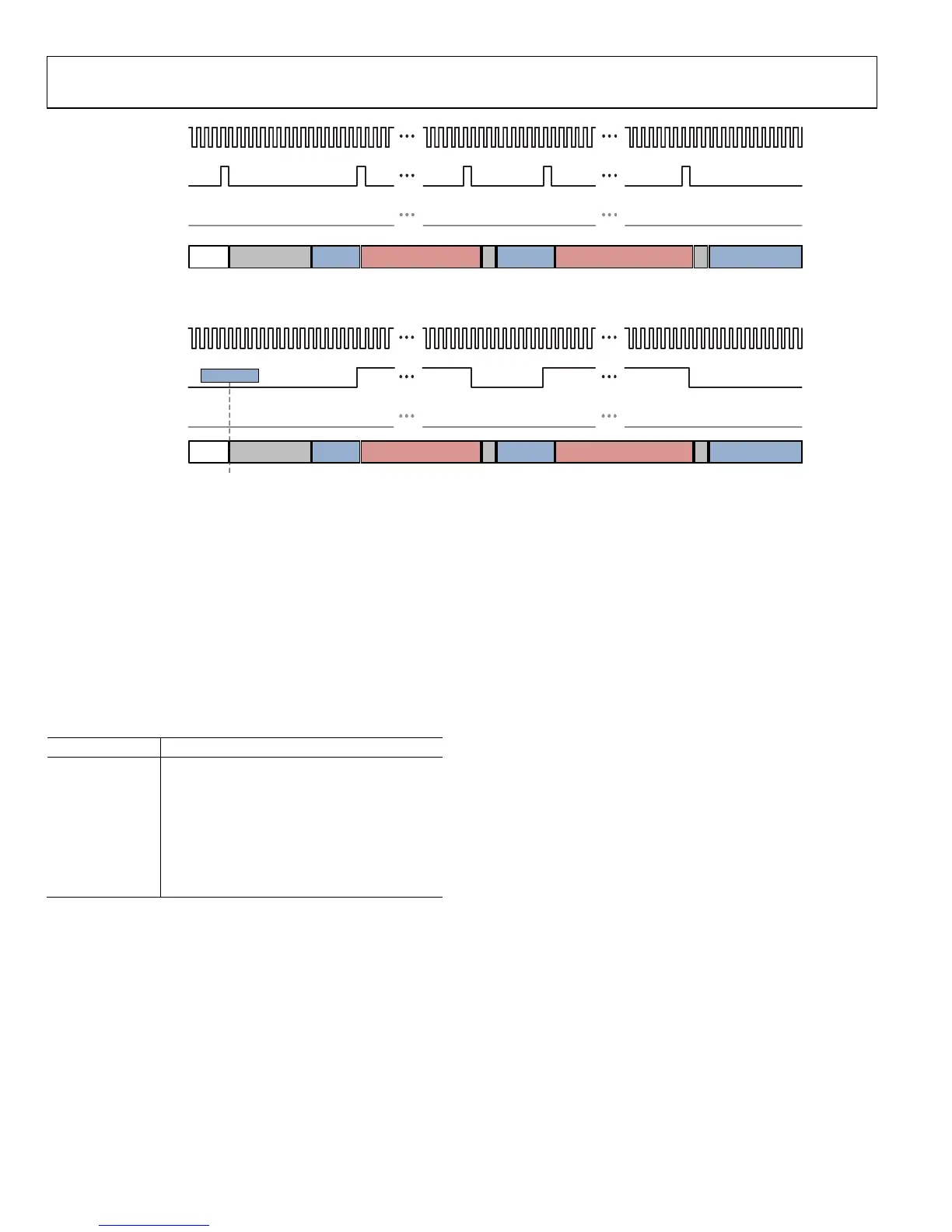

Figure 12. ENABLE

Pulse Mode, FDD (Minimum Pulse Width = One FB_CLK Cycle)

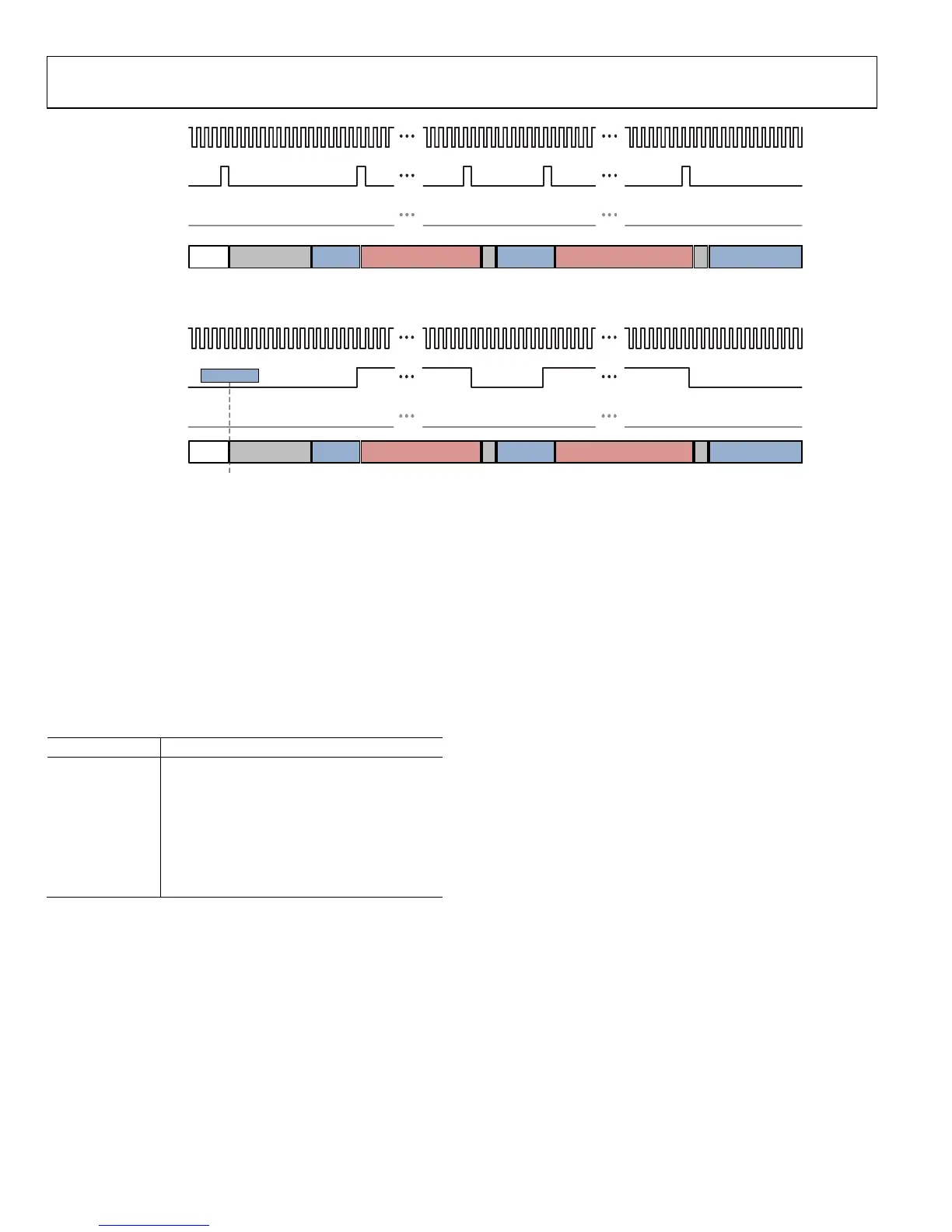

Figure 13. ENABLE Level M

ode, FDD

FDD Independent Control

When the AD9361 is in FDD mode, the FDD independent

control option allows the receive chain and transmit chain to be

enabled independently. This mode is enabled by setting the

FDD External Control Enable bit (0x015[D7]). Note that SPI

writes must be used to move the ENSM into the FDD state.

Then the ENABLE and TXNRX pins are internally remapped to

Force Rx On and Force Tx On, respectively. Once in the FDD

state, the control combinations in Table 14 are allowed.

Table 14. ENABLE/TXNRX Pin Alternative Functionality

Pin Level Description

ENABLE low,

TXNRX low

Rx and Tx signal chains disabled (Operates

like ALERT state)

ENABLE high,

TXNRX low

Rx signal chain enabled, Tx signal chain

disabled (Operates like Rx state)

ENABLE low,

TXNRX high

Rx signal chain disabled, Tx signal chain

enabled (Operates like Tx state)

ENABLE high,

TXNRX high

Rx signal chain enabled, Tx signal chain

enabled. (Operates like FDD state)

Note that since the ENSM always stays in the FDD state, it

never moves to the FDD FLUSH state. Therefore, the BBP must

allow enough time after enabling the receive chain for the

digital filters to flush, and enough time after sending Tx data

for the Tx to finish its transmission before disabling the

corresponding signal chain. If Tx_FRAME is held low, the data

port in the AD9361 will force zeros into the Tx data path.

Note that in pulse mode the BBP should send pulses on the

ENABLE pin to enable/disable the Rx signal chain. Pulses sent

on the TXNRX pin will enable/disable the Tx signal chain.

When using a SPI write to move from ALERT into the FDD

state, both the Rx and Tx signal chains start disabled until the

first pulse is received. The pulse should have a minimum pulse

width of one FB_CLK cycle. No maximum pulse width is

defined; the pulse is edge detected and internally generates a

one cycle wide pulse.

FB_CLK

ENABLE

TXNRX

ENSM STATE[3:0]

ALERTWAIT

POWER UP VCO

LDO

ALERT FDD ALERT FDD

11668-013

FB_CLK

ENABLE

TXNRX

ENSM STATE[3:0]

ALERTWAIT

POWER UP VCO

LDO

ALERT FDD ALERT FDD

SPIWRITE

11668-014

Loading...

Loading...