UG-570 AD9361 Reference Manual

| Page 46 of 128

When comparing the signal power with the energy lost threshold,

there is also a time factor as well. Each time the signal power

value updates, the AGC computes the difference between the

power measured at the beginning of gain lock and the current

signal power. This difference is compared against the Energy Lost

Threshold. If the difference exceeds the threshold for a time equal

to twice the Gain Lock Exit Count then the gain unlocks as

shown in Table 24. The Gain Lock Exit Count is clocked at the

ClkRF rate. The same comparison is made for the Stronger Signal

Threshold, which appears in Table 26.

The large ADC threshold is stored in Register 0x105 and the large

LMT threshold is stored in Register 0x108. For the peak

detectors, there are no time requirements. A single overload will

unlock the gain.

Generally, the AGC is the best arbiter of when the gain should

unlock. However, in some situations, it may be advantageous for

the BBP to initiate an unlock condition. If the BBP pulls the

EN_AGC pin high, the gain will unlock and the AGC algorithm

will restart. The BBP cannot force the gain to lock at a certain

time but it can control when the gain unlocks. Table 25 shows

how to use this feature.

If the thresholds are set correctly, the typical setup which unlocks

the gain when the AD9361 exits Rx mode or if the burst/subframe

ends is sufficient for most applications. However, if desired, it is

also possible to prevent the gain from unlocking in some

instances (see Table 26). The settings are dependent on whether

the BBP will use the EN_AGC pin to unlock the gain. If this is the

case, then the EN_AGC pin should be low except when the gain

should be unlocked. If the EN_AGC pin is not used, then the

Gain Lock Delay bit must be set high.

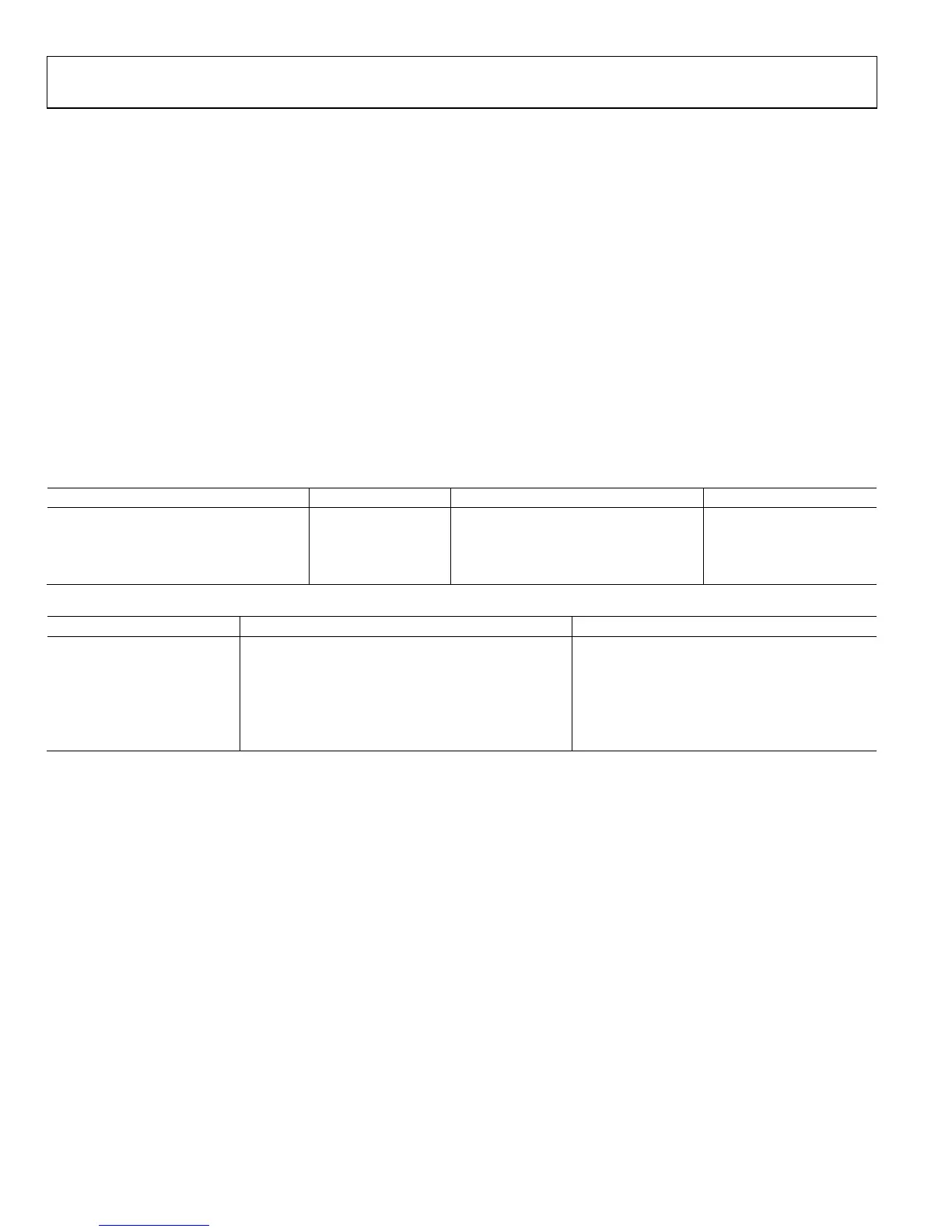

Table 25. Full List of Gain Unlock Conditions vs. Target Gain Index

Condition that Unlocks the Gain Gain Index Type Set Bits Clear Bits

EN_AGC pulled high Maximum gain 0x0FB[D6], 0x111[D5] 0x110[D6:D5]

EN_AGC pulled high Optimize gain 0x0FB[D6], 0x110[D6], 0x111[D5] 0x110[D5]

EN_AGC Pulled high No gain change 0x0FB[D6] 0x110[D5], 0x111[D5]

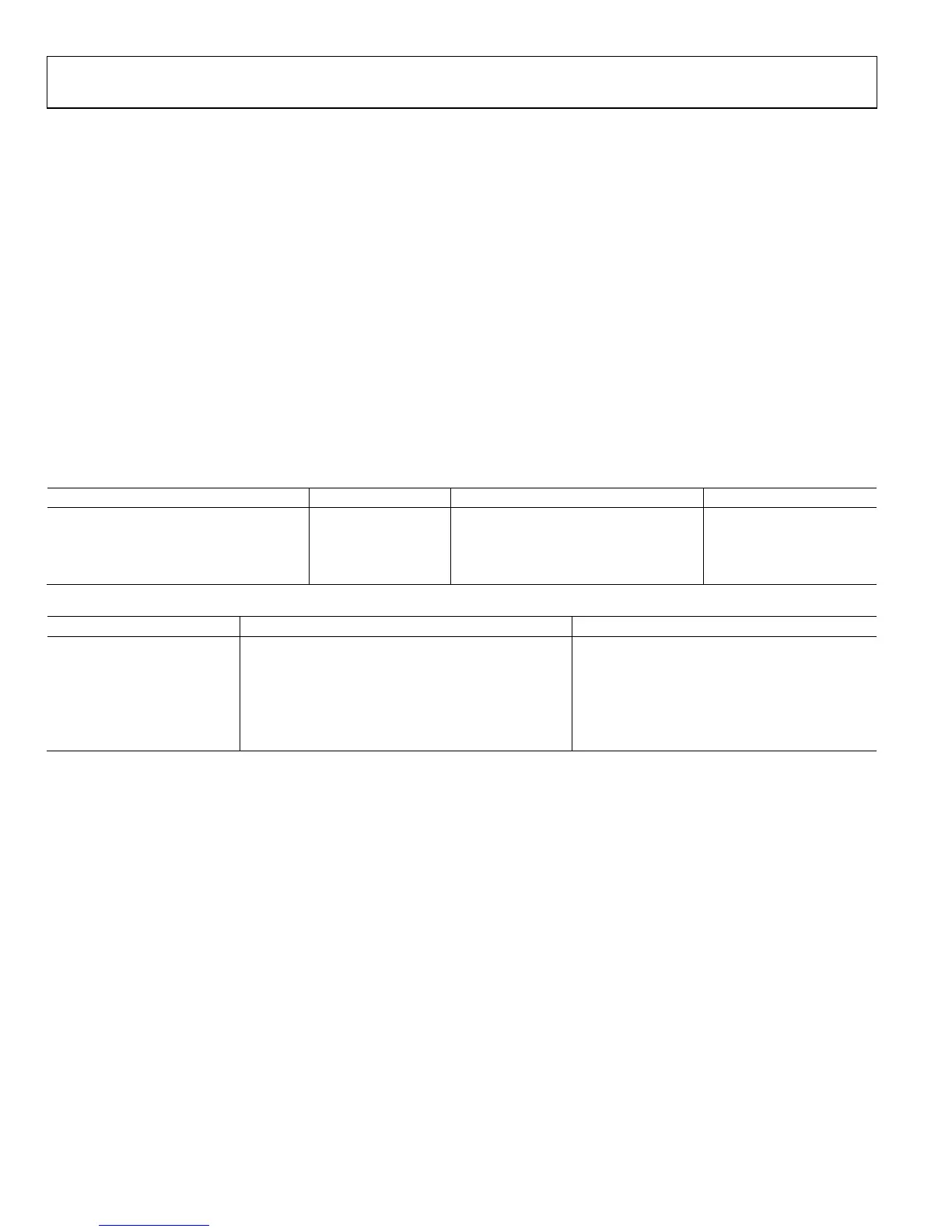

Table 26. Preventing Gain Unlock Conditions in State 5

If EN_AGC Pin Is Used Don’t Unlock Gain Even If: Set Bits

No Energy Lost Threshold Exceeded 0x0FB[D6], 0x014[D1], 0x110[D3]

No Stronger Signal Threshold Exceeded 0x0FB[D6], 0x014[D1], 0x115[D7]

No Large ADC or Large LMT Overload 0x0FB[D6], 0x014[D1], 0x110[D1]

Yes Energy Lost Threshold Exceeded 0x0FB[D6], 0x110[D3]

Stronger Signal Threshold Exceeded

Yes Large ADC or Large LMT Overload 0x0FB[D6], 0x110[D1]

Loading...

Loading...