CENTRAL PROCESSING UNIT MC68332

5-4 USER’S MANUAL

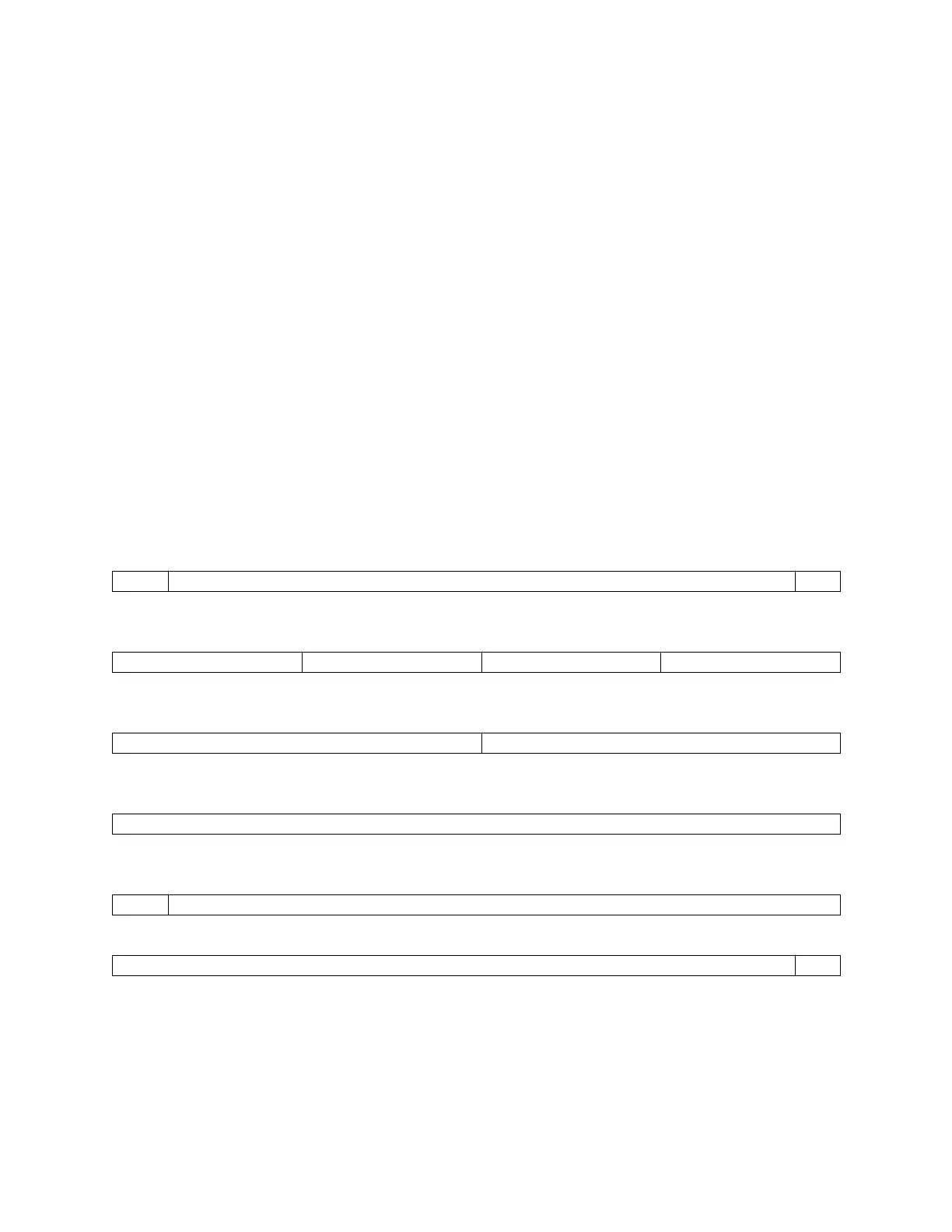

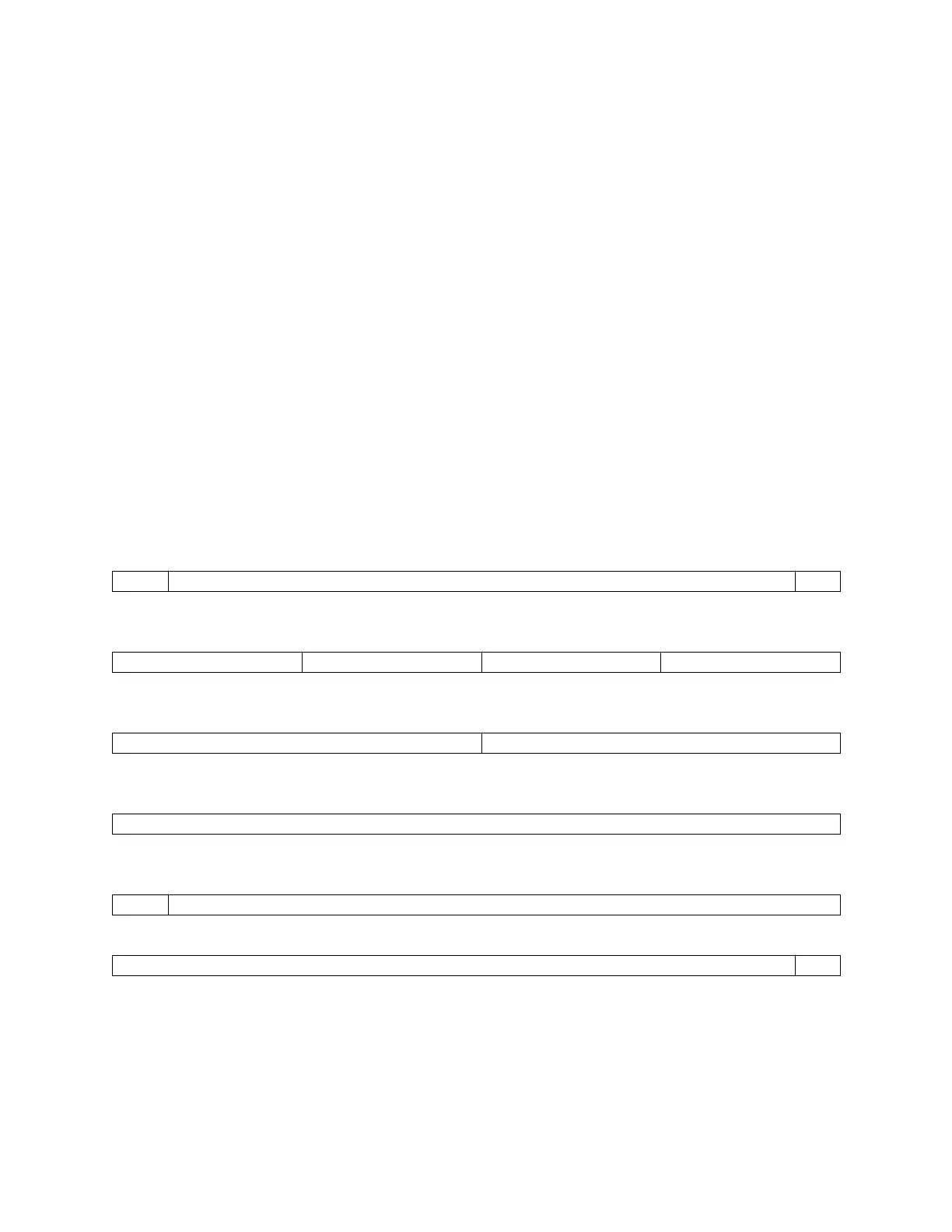

Each of data registers D7–D0 is 32 bits wide. Byte operands occupy the low-order 8

bits; word operands, the low-order 16 bits; and long-word operands, the entire 32 bits.

When a data register is used as either a source or destination operand, only the ap-

propriate low-order byte or word (in byte or word operations, respectively) is used or

changed; the remaining high-order portion is unaffected. The least significant bit (LSB)

of a long-word integer is addressed as bit zero, and the most significant bit (MSB) is

addressed as bit 31. Figure 5-4 shows the organization of various types of data in the

data registers.

Quad-word data consists of two long words and represents the product of 32-bit mul-

tiply or the dividend of 32-bit divide operations (signed and unsigned). Quad-words

may be organized in any two data registers without restrictions on order or pairing.

There are no explicit instructions for the management of this data type, although the

MOVEM instruction can be used to move a quad-word into or out of the registers.

Binary-coded decimal (BCD) data represents decimal numbers in binary form. CPU32

BCD instructions use a format in which a byte contains two digits. The four LSB con-

tain the least significant digit, and the four MSB contain the most significant digit. The

ABCD, SBCD, and NBCD instructions operate on two BCD digits packed into a single

byte.

Figure 5-4 Data Organization in Data Registers

31 30 1 0

MSB LSB

BYTE

31 24 23 16 15 8 7 0

HIGH-ORDER BYTE MIDDLE HIGH BYTE MIDDLE LOW BYTE LOW-ORDER BYTE

16-BIT WORD

31 16 15 0

HIGH-ORDER BYTE LOW-ORDER WORD

LONG-WORD

31 0

LONG-WORD

QUAD-WORD

63 62 32

MSB ANY Dy

31 1 0

ANY Dy LSB

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...