The program_flash function takes three arguments:

a.

The .rpd file to write to flash memory.

b. The start address.

c.

Number of words to write for each QSPI_WRITE command. The QSPI_WRITE supports up to 1024 words per write

instruction.

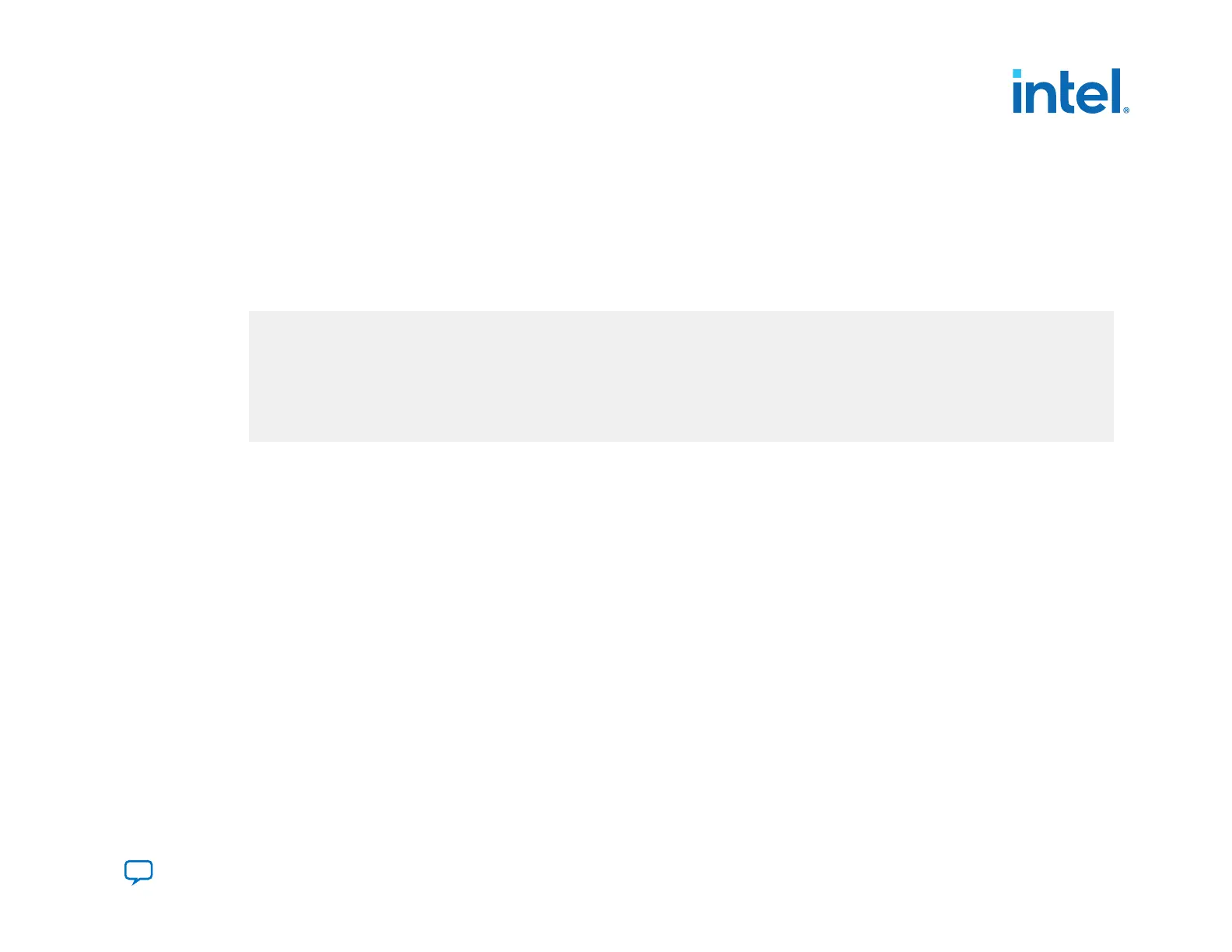

Figure 83. Program New Application Image

$ source rsu1.tcl

/channels/local/top/master_1

$ program_flash new_application_image.rpd 0x03ff0000 1024

total number of words is 584704

total number of page is 571

total number of sector is 36

reading rpd is completed

start writing flash

writing flash is completed

3. Write the new application image start address to a new image pointer entry in the configuration firmware pointer block

(CPB) using the QSPI_WRITE command. Ensure that the new image pointer entry value is 0xFFFFFFFF before initiating

the write.

Note: When using HPS to manage RSU, you must update both copies of the Configuration Pointer Block (CPB0 and CPB1)

and the sub-partition table (SPT). In a non-HPS case, while updates to both copies of the pointer blocks are

mandatory, the updates to the sub-partition table are not required. For more details about the SPT and CPB, refer

to Table 47 on page 176 for the sub-partition table layout and Table 50 on page 178 for the pointer block layout.

Based on the example described above, the address offset 0x20 in the CPB0 and CPB1 must point to the start address of the

application image. The next new image pointer entry value must be 0xFFFFFFFF before you write the start address of the

new application image to the next image pointer entry.

You can use the QSPI_read function verify that the new image pointer entry value is 0xFFFFFFFF . The QSPI_read function

takes in two arguments:

1. Start address

2. Number of words to read

5. Remote System Update (RSU)

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

203

Loading...

Loading...