FX Series Programmable Controllers Execution Times And Instructional Hierarchy 7

7-2

Note 1:

•“n” in the formulae to calculate the ON/OFF execution time, refers to the number of STL

instructions at the current parallel/merge branch. Thus the value of “n” will fall in the

range 1 to 8.

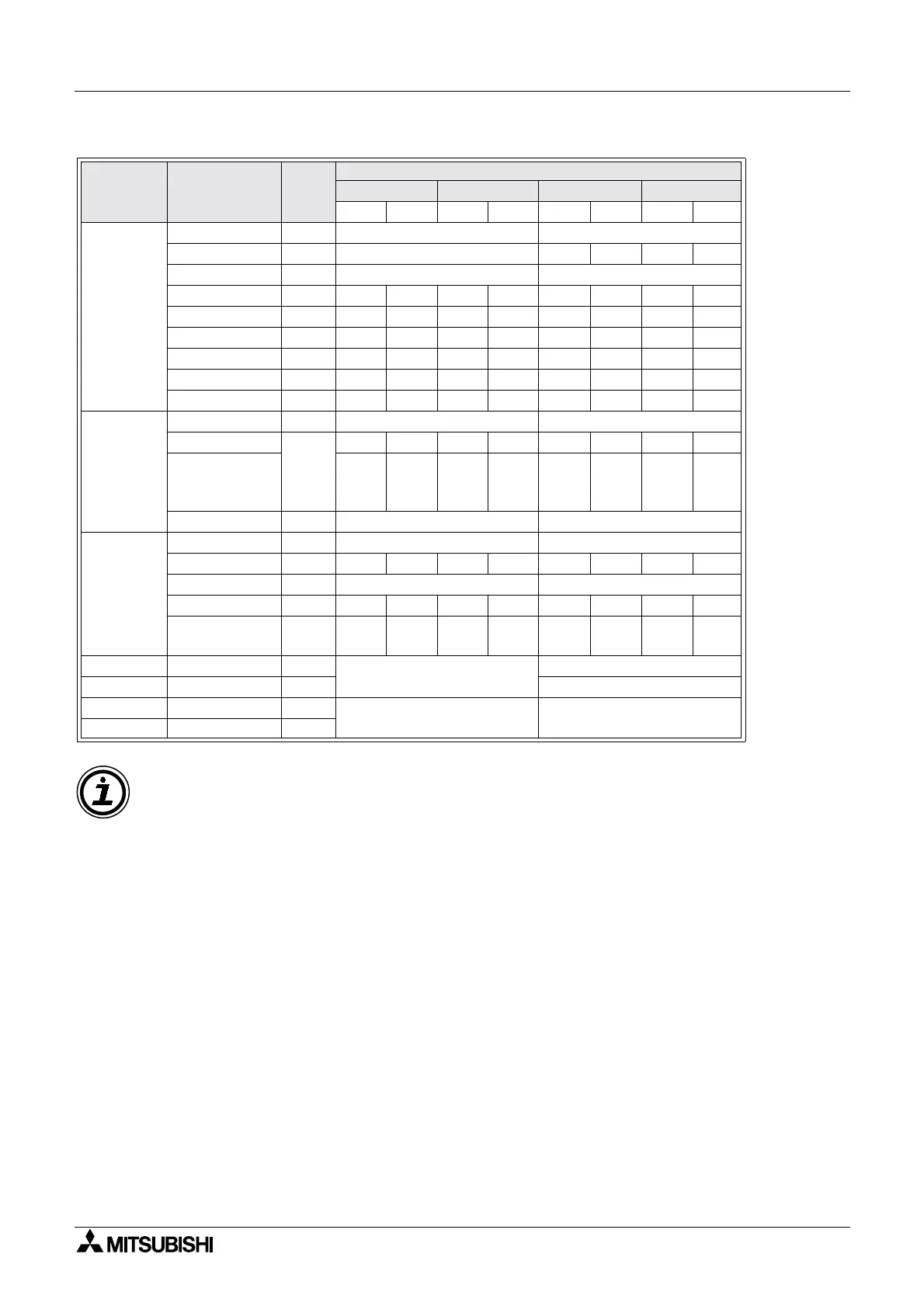

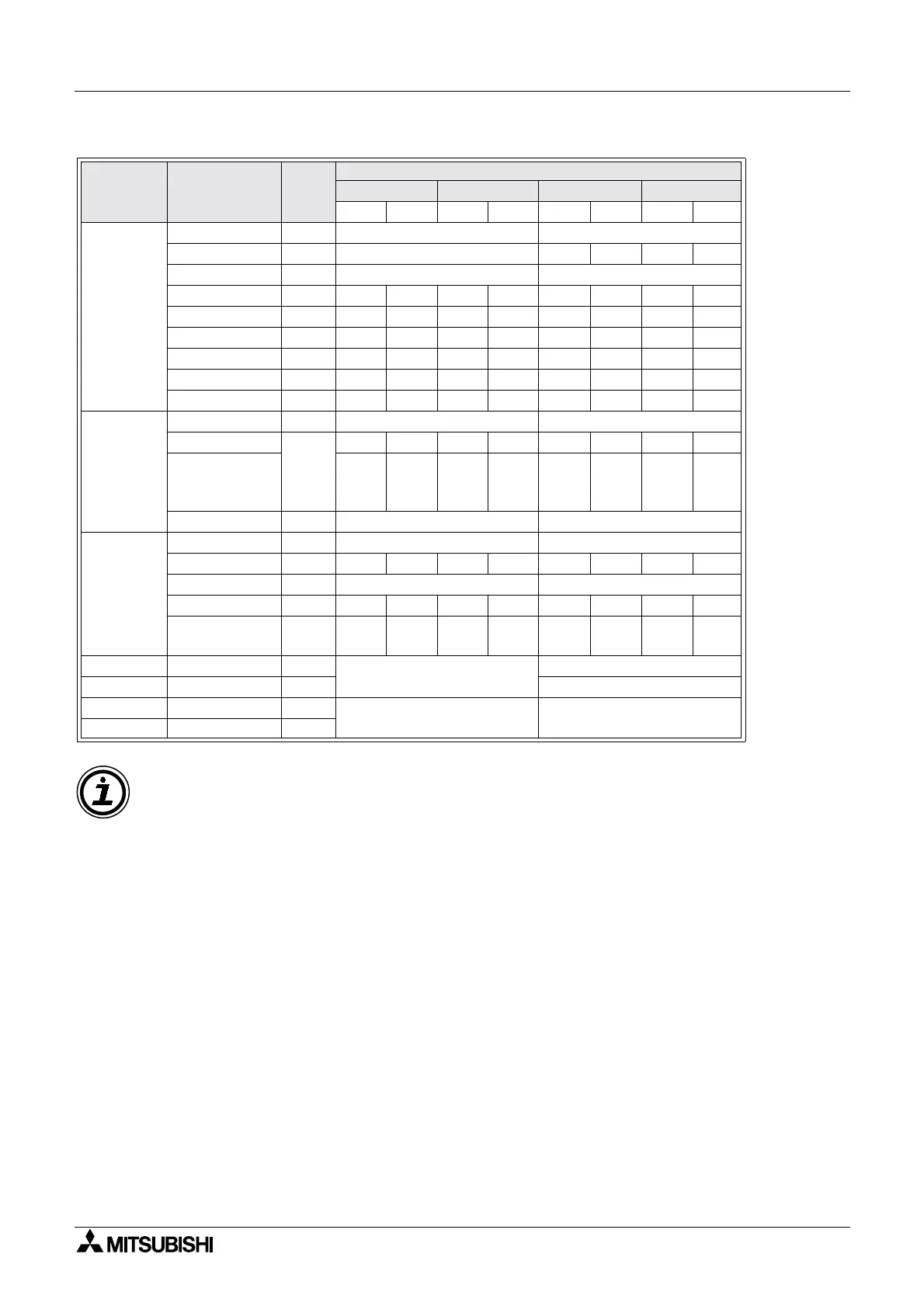

Mnemonic

Object

Devices

Steps

Execution Time in µsec

FX1S FX1N FX2N FX2NC

ON OFF ON OFF ON OFF ON OFF

OUT

Y, M 1 0. 7 0 .0 8

S 2 4.4 24.4 24.3 24.4 24.3

Special M 2 2.8 0.16

T-K 3 11.2 10.2 11.2 10.2 42.3 37.4 42.3 37.4

T-D 3 12.2 11.2 12.2 11.2 42.2 37.2 42.2 37.2

C-K (16 bit) 3 8.1 6.9 8.1 6.9 25.5 24.9 25.5 24.9

C-D (16 bit) 3 9.5 8.0 9.5 8.0 25.3 25.0 25.3 25.0

C-K (32 bit) 5 8.1 6.8 8.1 6.8 25.3 24.9 25.3 24.9

C-D (32 bit) 5 9.5 8.0 9.5 8.0 25.2 24.9 25.2 24.9

SET

Y, M 1 0.85 0.08

S

2

4.2 2.4 4.2 2.4 23.7 17.2

S whenusedin

an STL step

(see note 1)

18.6+

6.8n

2.4

18.6+

6.8n

2.4

27.3+

12.6n

17.2

27.3+

12.6n

17.2

Special M 2 2.8 0.16

RST

Y, M 1 0.85 0.08

S 2 3.8 2.4 3.8 2.4 23.1 17.3 23.1 17.3

Special M 2 2.8 0.16

T, C 2 8.7 7.3 8.7 7.3 27 25 27 25

D, V, Z and

special D

3 3.8 1.1 3.8 1.1 21.9 17.1 21.9 17.1

PLS Y, M 2

10.8

0.32

PLF Y, M 2 0.32

P0TO631

0.45 0.08

IIooo 1

Loading...

Loading...