RL78/G13 CHAPTER 19 RESET FUNCTION

R01UH0146EJ0100 Rev.1.00 871

Sep 22, 2011

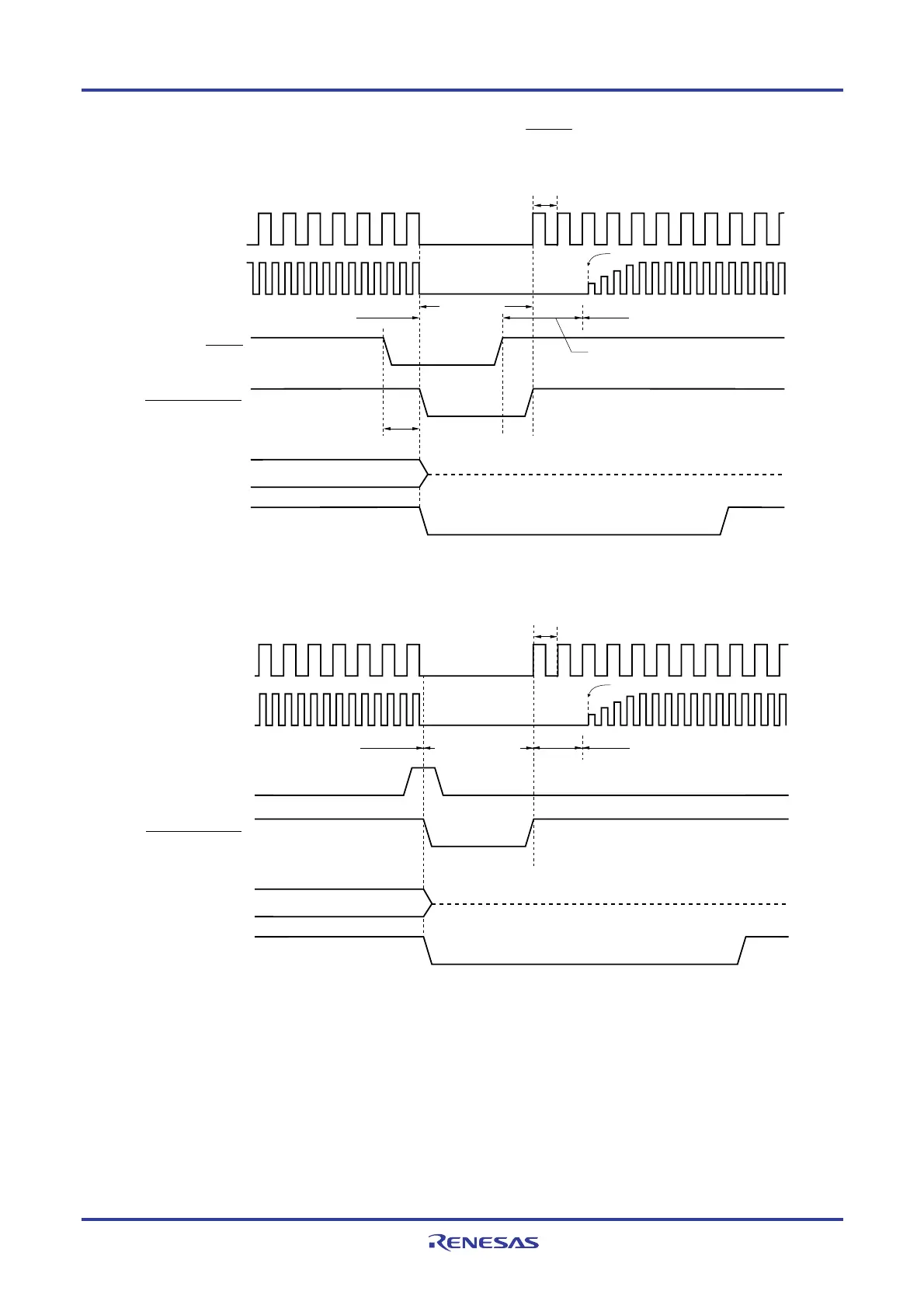

Figure 19-2. Timing of Reset by RESET Input

Delay

Hi-Z

Normal operationCPU status

Normal operation

(high-speed on-chip oscillator clock)

RESET

Internal reset signal

Port pin

(except P130)

Port pin

(P130)

Note

High-speed system clock

(when X1 oscillation is selected)

High-speed on-chip

oscillator clock

Starting X1 oscillation is specified by software.

Reset processing : 387 to 674 μs (When LVD is used)

155 to 360 μs (When LVD off)

Wait for oscillation

accuracy stabilization

Reset period

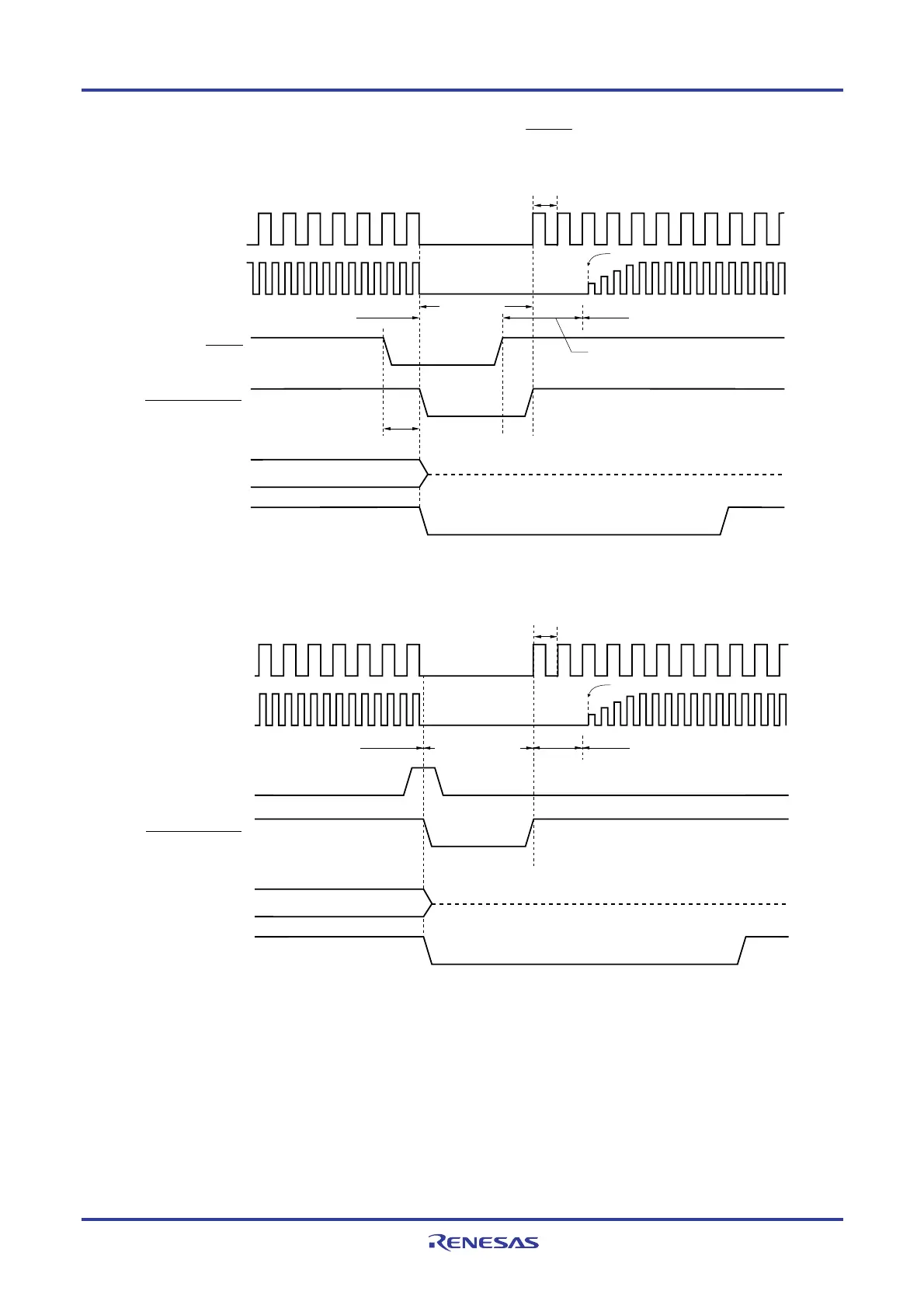

Figure 19-3. Timing of Reset Due to Execution of Illegal Instruction or Watchdog Timer Overflow

Normal operation

Reset period

(oscillation stop)

CPU status

Execution of Illegal

Instruction/

Watchdog timer

overflow

Internal reset signal

Hi-Z

Note

High-speed system clock

(when X1 oscillation is selected)

High-speed on-chip

oscillator clock

Starting X1 oscillation is specified by software.

Normal operation

(high-speed on-chip oscillator clock)

Wait for oscillation

accuracy stabilization

Reset processing

Port pin

(except P130)

Port pin

(P130)

41 to 69 μs

Note When P130 is set to high-level output before reset is effected, the output signal of P130 can be dummy-output

as a reset signal to an external device, because P130 outputs a low level when reset is effected. To release a

reset signal to an external device, set P130 to high-level output by software.

Caution A watchdog timer internal reset resets the watchdog timer.

<R>

<R>

Loading...

Loading...