4.17

Date Code 20170601 Instruction Manual SEL-387-0, -5, -6 Relay

Control Logic

Trip and Close Logic

Trip Logic

There are five specific sets of trip logic within the SEL-387. They are

designed to operate when SEL

OGIC control equation trip variable setting TRm

is asserted (m = 1, 2, 3, 4, 5) and to unlatch when SEL

OGIC control equation

setting ULTRm is asserted. The output of the logic is Relay Word bit TRIPm.

The logic operates much like the Latch Bit function in SEL

OGIC Control

Equation Sets 1 through 3, with additional characteristics. In the trip logic, the

set or latch function has priority over the reset or unlatch function.

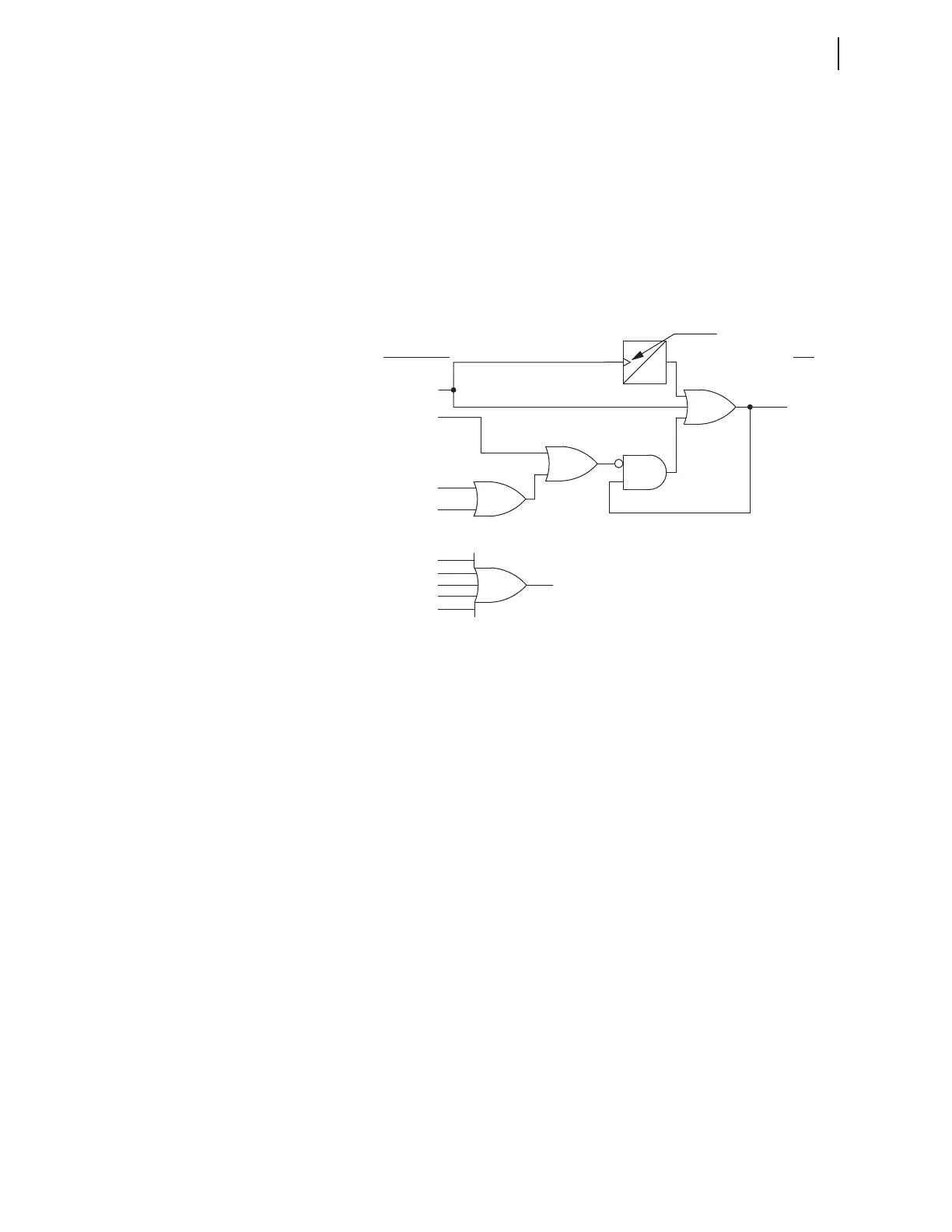

Figure 4.7 shows the logic diagram for the TRIP1 logic. The remaining logic

for TRIP2 through TRIP5 is identical, using variables TR2 through TR5 and

ULTR2 through ULTR5, respectively.

Figure 4.7 SEL-387 Trip Logic (TRIP1)

The logic begins with the assertion of SELOGIC control equation TR1, one of

the Group variables. In our example application, Relay Word bits representing

three Winding 1 overcurrent elements and the OPE 1 command are used to

assert TR1. TR1 directly asserts TRIP1 via the three-input OR gate at the

right.

However, TR1 may only assert briefly while a more lengthy assertion of

TRIP1 is needed. There are two means to ensure a longer TRIP1 assertion. At

the top of the diagram is an Edge Trigger Timer. It detects the rising edge of

TR1, and issues a second output to the OR gate. This second output will last

the duration of Group setting TDURD (minimum trip duration timer). Once

the rising edge has been detected and the timing started, the ongoing state of

the TR1 input to the timer is ignored. Thus, TRIP1 will be asserted for a

minimum of TDURD cycles, even if TR1 is asserted for as little as one

processing interval, or if the unlatch portion of the logic is asserted before

TDURD expires. The default setting of TDURD is nine cycles.

TRIP1 also seals itself in via the AND gate at the bottom. This AND gate

receives the negated inputs from the unlatching functions. As long as no

unlatch function is asserted, the seal of TRIP1 remains intact. TRIP1 is used to

drive an output contact to initiate tripping of the breaker or breakers. In our

example, OUT101 = TRIP1.

The unlatching of the trip logic is accomplished via three means. The first is

the assertion of the SEL

OGIC control equation setting ULTR1. In our example,

ULTR1 = !50P13 = NOT 50P13. This current element is set to pick up at

0.5 A. Thus, ULTR1 asserts when the currents in all three phases drop below

0.5 A, indicating successful three-pole opening of the breaker.

Relay

Word

Bit

TDURD

O

TR1

ULTR1

TRIP1

(in) (out)

rising

edge detect

Minimum Trip

Duration Timer

TRIPL

TRGTR

TAR R

Serial Port Command

{TARGET RESET}

Pushbutton

TRIP1

TRIP5

TRIP4

TRIP3

TRIP2

SELOGIC Control

Equation Settings

Loading...

Loading...