Go back to top Go back to ToC

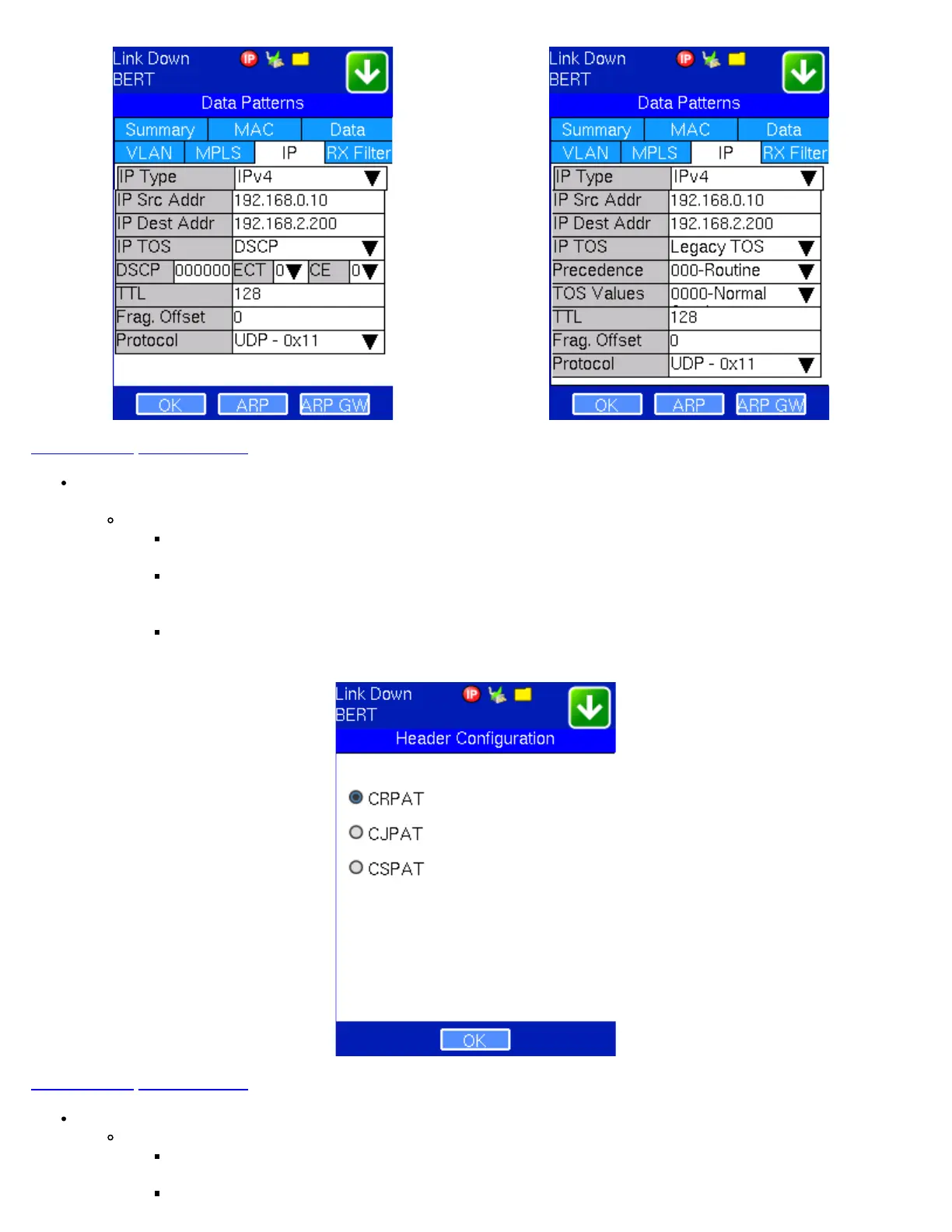

Data Tab: User selects a test pattern that will be encapsulated in the Ethernet frame payload (for framed mode).

Depending on the test layer, different test pattern options are available;

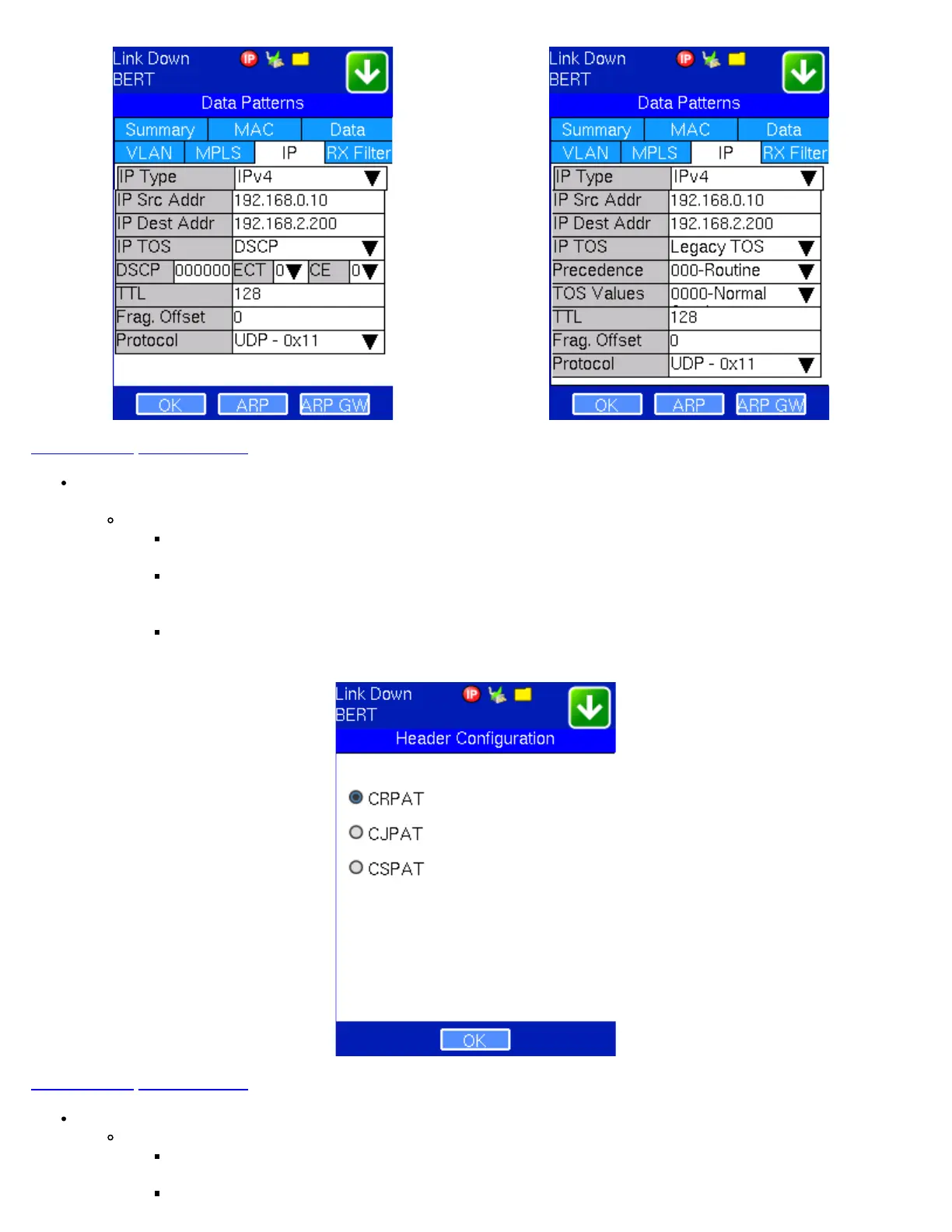

Layer 1 test patterns:

CRPAT: Compliant Random Pattern provides broad spectral content and minimal peaking for the

measurement of jitter at component or system level.

CJTPAT: Compliant Jitter Test Pattern is a Jitter Tolerance Pattern that stresses a receiver by exposing it to

extreme phase jumps thereby stressing the Clock Data Recovery (CDR) circuitry. The pattern alternates

between repeating low transition density patterns and repeating high transition density patterns.

CSPAT

BERT Setup - Test Pattern (Layer 1 Framed)

Go back to top Go back to ToC

Layer 2 & 3 test patterns:

PRBS:

2^31 -1 (147 483 647-bit pattern used for special measurement tasks, e.g. delay measurements at higher bit

rates)

2^23 -1 (8 388 607-bit pattern primarily intended for error and jitter measurements at bit rates of 34 368 and

TX130M+_e-manual_D07-00-051P_RevD00

Loading...

Loading...