2 3 4

Meaning

o

o

Processor

Interface

detected

parity

error on

returned

status

and/or

condition

code.

The

result of

the

TDY

is

indeterminate.

o 0

I/O

address not

recognized,

TDY

not

ac-

cepted,

and

status information

returned

to

the

general

registers is

incorrect.

o

No

I/o

address

recognized

and

TDY

aborted

because

an

error

detected

when

the

lOP

at-

tempted

to

read

and

transfer

the

TDY

param-

eters

(device/device

controller

address

and

R field information) from the

BP

to

the

lOP

via

main memory.

No

status information

re-

turned

to

general

registers.

If

CC4 = 1,

the

MIOP is in

the

test

mode

and

the

meaning

of

the

condition

code

during a

TDY

is:

2 3 4

Meaning

0

0 0

Unit is performing

an

Order

Out

operation.

0 0

Unit is performing

an

Order

In

operation.

0 0

Unit

is

performing a Data

Out

operation.

0

Parity

error

detected

by Processor

Interface

on

returned

status

and/or

condition

code.

The

result of

the

TDY

is

indeterminate.

0 Unit is performing a Data In

operation.

BCF

detected

while

unit

performing a Data

In

operati

on.

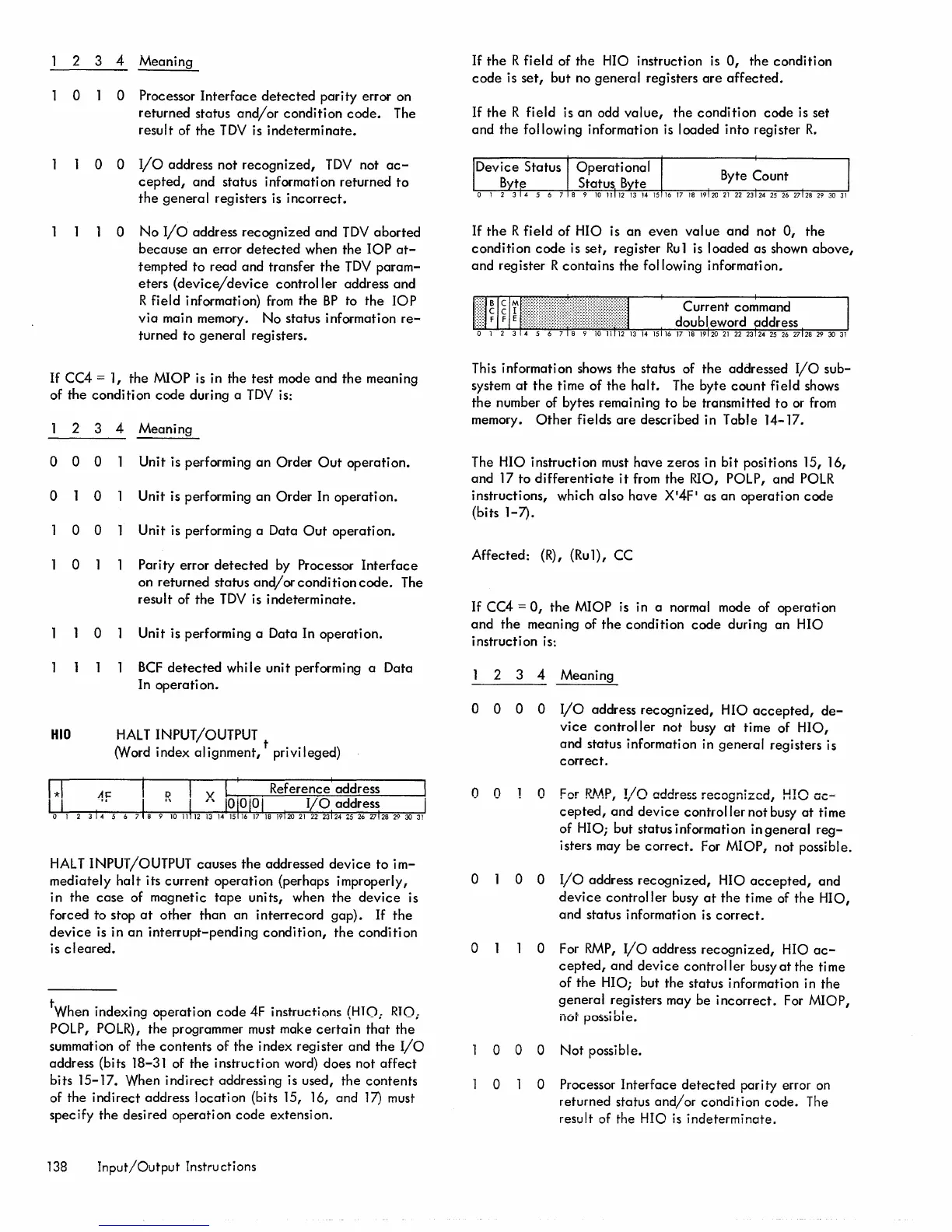

HIO

HAL

T INPUT/OUTPUT

0/Vord

index

alignment,

t privileged)

HALT

INPUT/OUTPUT

causes

the

addressed

device

to

im-

mediately

halt

its

current

operation

(perhaps improperly,

in

the

case

of

magnetic

tape

units, when

the

device

is

forced to stop

at

other

than

an i nterrecord

gap).

If

the

device

is in

an

interrupt-pending

condition,

the

condition

is

cleared.

t

When

indexing

operation

code

4F instructions (HIO; RIO;

POLP, POLR),

the

programmer must make

certain

that

the

summation of

the

contents

of

the

index

register and

the

I/o

address (bits 18-31 of

the

instruction word) does not

affect

bits 15-17. When

indirect

addressing is used,

the

contents

of

the

indirect

address

location

(bits 15, 16,

and

17)

must

specify

the

desired

operation

code

extension.

138

Input/Output

Instructions

If

the

R

field

of

the

HIO instruction

is

0,

the

condition

code

is

set,

but

no

general

registers

are

affected.

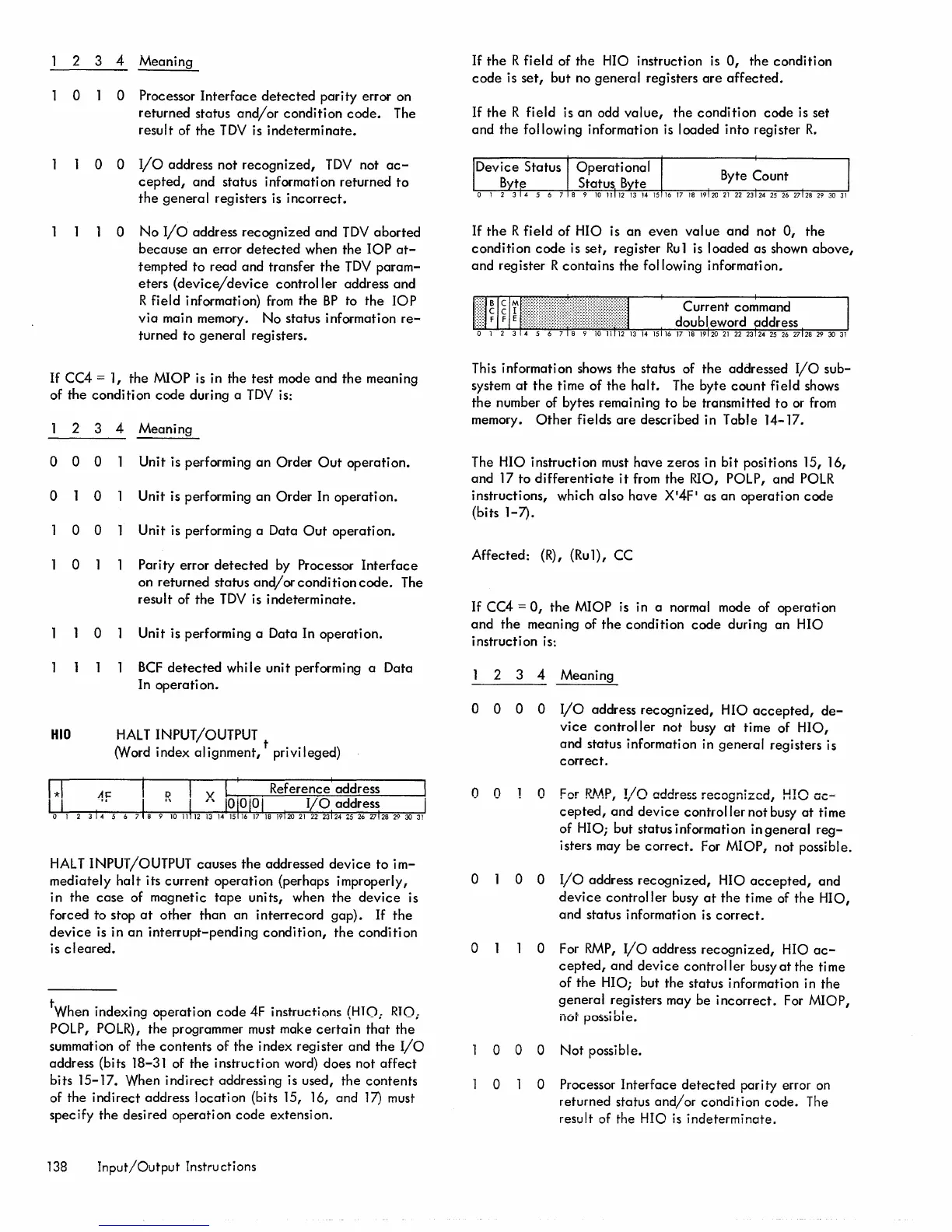

If

the

R

field

is

an

odd

value,

the

condition

code

is set

and

the following information is loaded

into

register

R.

If

the

R

field

of HIO is

an

even

value

and

not

0,

the

condition

code

is

set,

register

Ru

1 is

loaded

as

shown

above,

and

register R

contains

the

following information.

This information shows

the

status of

the

addressed

I/O

sub-

system

at

the

time

of

the

halt.

The

byte

count

field

shows

the

number of bytes remaining

to

be transmitted

to

or from

memory.

Other

fields

are

described in Table

14-17.

The HIO instruction must

have

zeros

in

bit

positions 15, 16,

and

17

to

differentiate

it

from

the

RIO, POLP, and

POLR

instructions, which

also

have X'4F' as

an

operation

code

(bits

1-7).

Affected: (R), (Ru1), CC

If

CC4 =

0,

the

MIOP is in a normal mode of

operation

and

the

meaning of

the

condition

code

during

an

HIO

instruction is:

2 3 4 Meaning

o 0 0 0

I/O

address

recognized,

HIO

accepted,

de-

vice

controller

not busy

at

time of

HIO,

and

status information in

general

registers is

correct.

o 0 0 For

R.MP,

I/O

address

recognized,

HIO ac=

o

o

cepted,

and

device

controller

not busy

at

time

of

HIO; but status information

ingeneral

reg-

isters may be

correct.

For

MIOP,

not possible.

o 0

I/O

address

recognized,

HIO

accepted,

and

device

controller

busy

at

the

time

of

the

HIO,

and

status i nformati on is

correct.

o For

RMP,

I/O

address

recognized,

HIO

ac-

cepted,

and

device

controller

busy

at

the time

of

the

HIO; but

the

status information in

the

general

registers may be

incorrect.

For MIOP,

not pO$5ible.

o 0 0

Not

possible.

o 0 Processor

Interface

detected

parity

error on

returned status

and/or

condi ti on

code.

The

result of the

HIO

is

indeterminate.

Loading...

Loading...