KCU116 Board User Guide 39

UG1239 (v1.2) September 28, 2018 www.xilinx.com

Chapter3: Board Component Descriptions

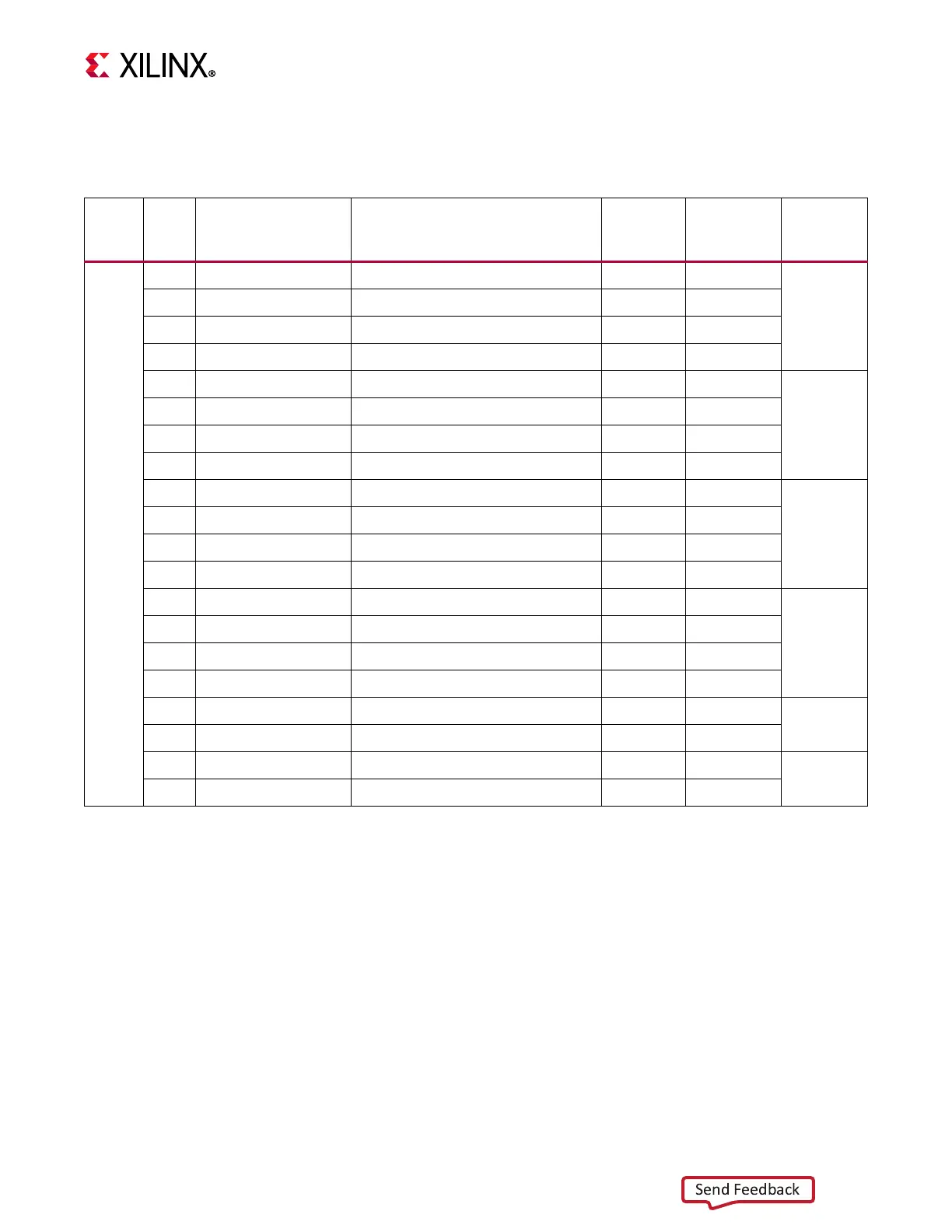

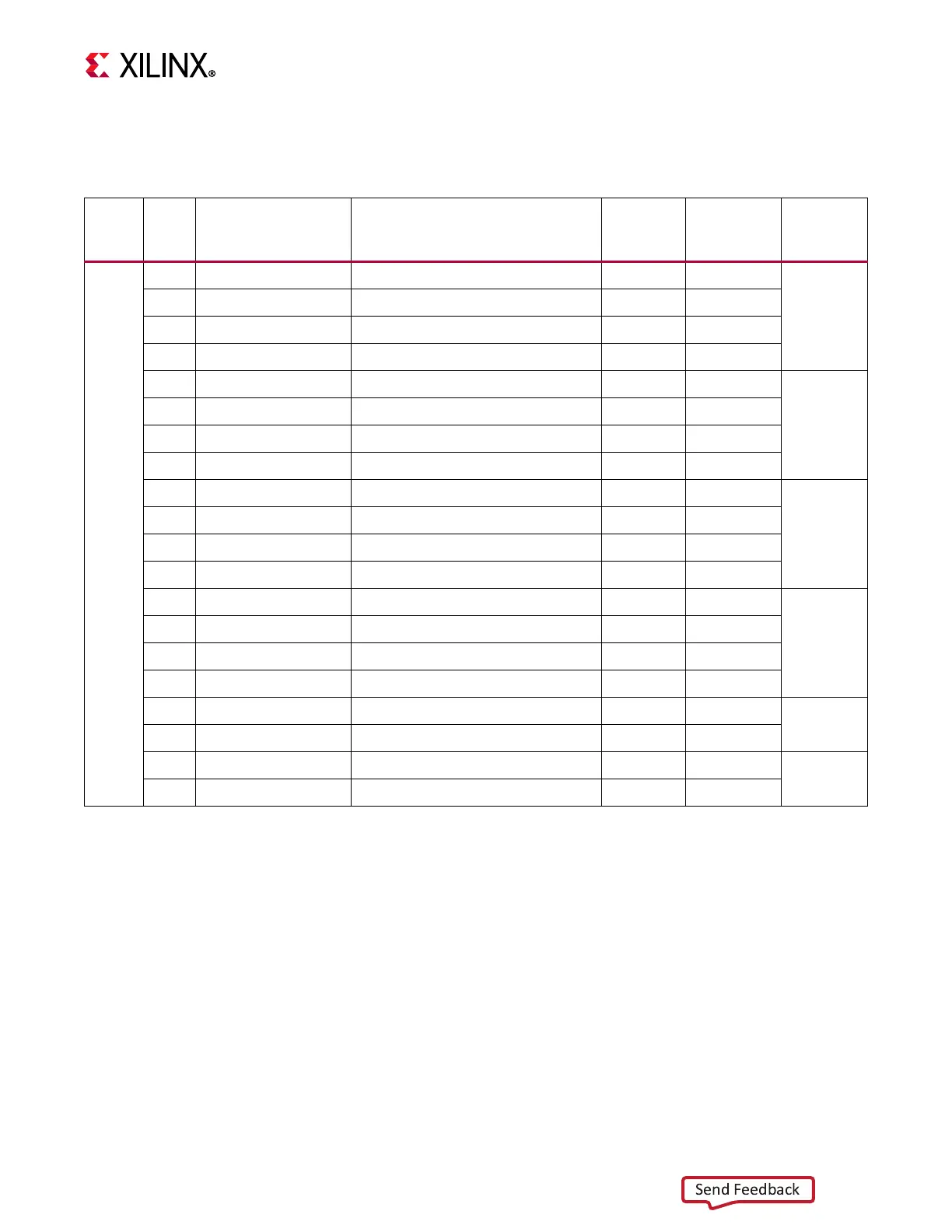

Table 3-8 lists the GTY Bank 226 interface connections between FPGA U1 and the four zSFP

connectors J1, J3, J4 and J6.

Table3‐8: KCU116 FPGA U1 GTY Bank 226 Connections

GTY

Bank

FPGA

(U1)

Pin

FPGA (U1) Pin Name Schematic Net Name

Connected

Pin

Connected

Pin Name

Connected

Device

GTY

Bank

226

N5 MGTYTXP0_226 SFP0_TX_P 18 TD_P

SFP0 J1

N4 MGTYTXN0_226 SFP0_TX_N 19 TD_N

M2 MGTYRXP0_226 SFP0_RX_P 13 RD_P

M1 MGTYRXN0_226 SFP0_RX_N 12 RD_N

L5 MGTYTXP1_226 SFP1_TX_P 18 TD_P

SFP1 J3

L4 MGTYTXN1_226 SFP1_TX_N 19 TD_N

K2 MGTYRXP1_226 SFP1_RX_P 13 RD_P

K1 MGTYRXN1_226 SFP1_RX_N 12 RD_N

J5 MGTYTXP2_226 SFP2_TX_P 18 TD_P

SFP2 J4

J4 MGTYTXN2_226 SFP2_TX_N 19 TD_N

H2 MGTYRXP2_226 SFP2_RX_P 13 RD_P

H1 MGTYRXN2_226 SFP2_RX_N 12 RD_N

G5 MGTYTXP3_226 SFP3_TX_P 18 TD_P

SFP3 J6

G4 MGTYTXN3_226 SFP3_TX_N 19 TD_N

F2 MGTYRXP3_226 SFP3_RX_P 13 RD_P

F1 MGTYRXN3_226 SFP3_RX_N 12 RD_N

P7 MGTREFCLK0P_226 SFP_SI5328_OUT_C_P

(1)

28 CKOUT1_P

SI5328B

U20

P6 MGTREFCLK0N_226 SFP_SI5328_OUT_C_N

(1)

29 CKOUT1_N

M7 MGTREFCLK1P_226 USER_MGT_SI570_CLOCK_C_P

(1)

4OUT

SI570 U56

M6 MGTREFCLK1N_226 USER_MGT_SI570_CLOCK_C_N

(1)

5OUT_B

Notes:

1. Series capacitor AC coupled.

2. MGT connections I/O standard not applicable.

Loading...

Loading...