MIPI CSI-2 RX Subsystem v4.0 11

PG232 July 02, 2019 www.xilinx.com

Chapter 1: Overview

Pixel Packing for Embedded Non-Image Data Types

AXI4-Stream TDATA width is based on main data type selected from the Vivado® IDE. The

position of embedded non-image data type bytes on emb_nonimg_tdata are listed

below:

• 1st byte on emb_nonimg_tdata[7:0]

•2nd byte on emb_nonimg_tdata[15:8] and so on.

Pixel Packing When Video Format Bridge is Not Present

The width of the data port in the video_out can be selected from Vivado IDE, under CSI-2

Options TDATA width. MIPI CSI-2 RX Subsystem follows the Recommended Memory Storage

section of the MIPI CSI-2 specifications to output pixels, when a video format bridge is not

present.

For more information the data type packing, refer MIPI Alliance Standard for Camera Serial

Interface CSI-2 Specification [Ref 1].

Example

Pixel mapping for different data types are shown in the following table:

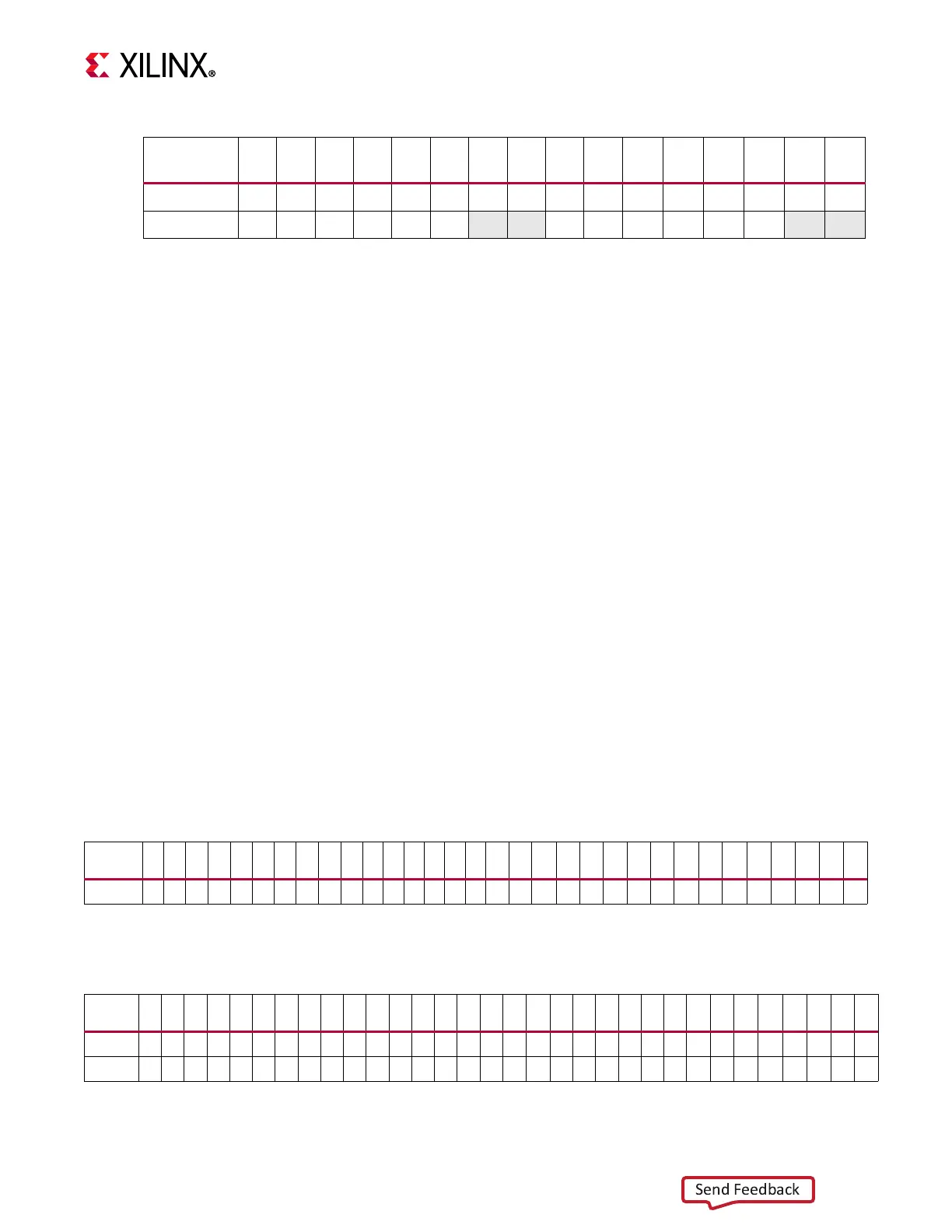

Table 1-3: Pixel Packing for RAW8 and RAW6 Data Types

Bit

Positions

151413121110987654 3 2 1 0

RAW8

q7 q6 q5 q4 q3 q2 q1 q0 p7 p6 p5 p4 p3 p2 p1 p0

RAW6

q5 q4

q3 q2 q1 q0

p5 p4 p3 p2 p1 p0

Notes:

1. p0 to p7 is the 1st pixel bits of RAW8; q0 to q7 is the 2nd pixel bits of RAW8.

2. p0 to p5 is the 1st pixel bits of RAW6; q0 to q5 is the 2nd pixel bits of RAW6.

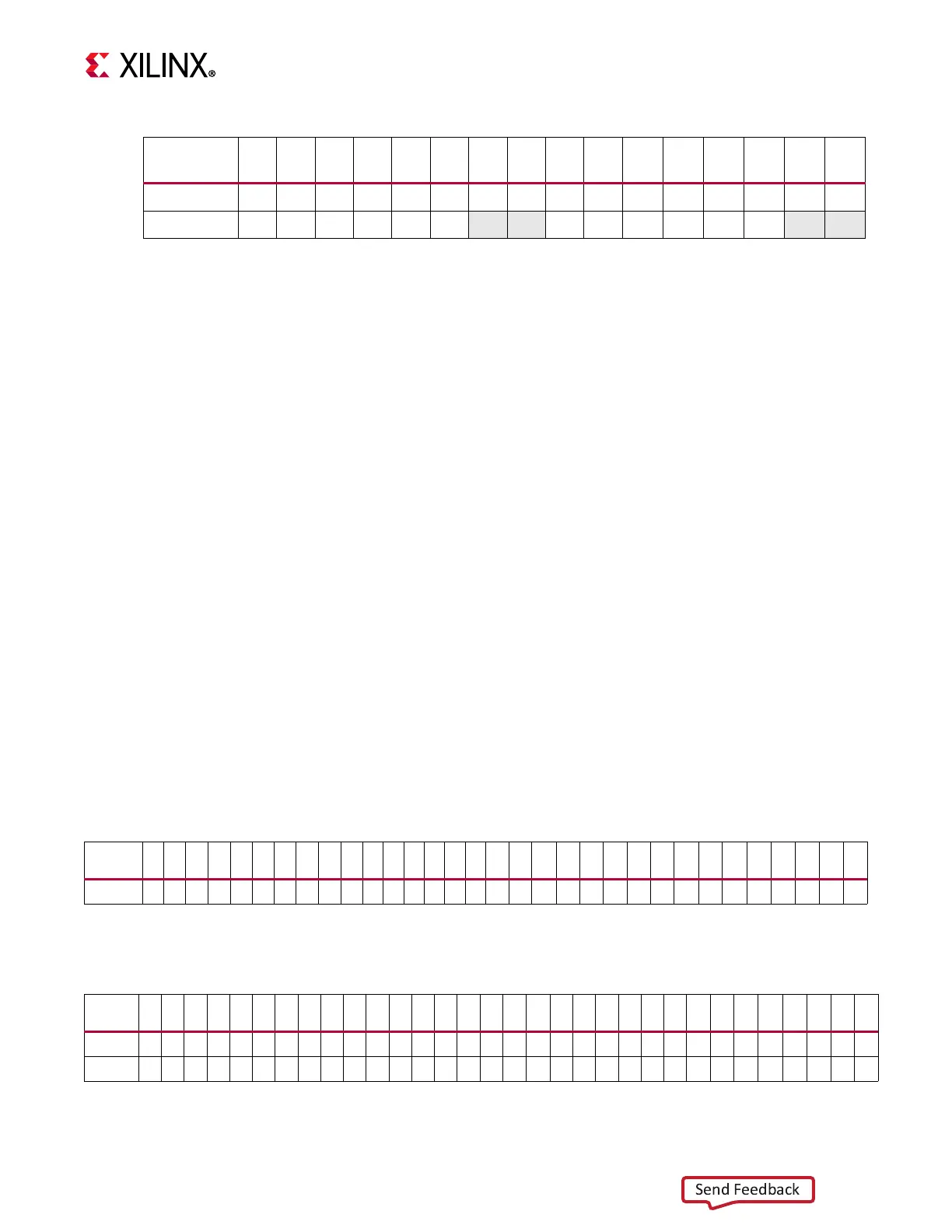

Table 1-4: Pixel Packing for RAW8 Data Type

Bit

Position

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RAW8

s7 s6 s5 s4 s3 s2 s1 s0 r7 r6 r5 r4 r3 r2 r1 r0 q7 q6 q5 q4 q3 q2 q1 q0 p7 p6 p5 p4 p3 p2 p1 p0

Notes:

1. p0 to p7 is the 1st pixel bits of RAW8; q0 to q7 is the 2nd pixel bits of RAW8.

Table 1-5: Pixel Packing for RAW10 Data Type

Bit

Position

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RAW10

s9 s8 s7 s6 s5 s4 s3 s2 r9 r8 r7 r6 r5 r4 r3 r2 q9 q8 q7 q6 q5 q4 q3 q2 p9 p8 p7 p6 p5 p4 p3 p2

RAW10

v9 v8 v7 v6 v5 v4 v3 v2 u9 u8 u7 u6 u5 u4 u3 u2 t9 t8 t7 t6 t5 t4 t3 t2 s1 s0 r1 r0 q1 q0 p1 p0

Loading...

Loading...