MIPI CSI-2 RX Subsystem v4.0 26

PG232 July 02, 2019 www.xilinx.com

Chapter 2: Product Specification

Global Interrupt Enable Register

The Global Interrupt Enable register is described in Tabl e 2- 1 1.

Interrupt Status Register

The Interrupt Status register (ISR) is described in Tabl e 2- 1 2 and captures the error and

status information for the core.

1 Stream Line buffer Full 0x0 R

Indicates the current status of line buffer

full condition

0

Soft reset/Core disable

in progress

0x0 R

Set to 1 by the core to indicate that

internal soft reset/core disable activities

are in progress

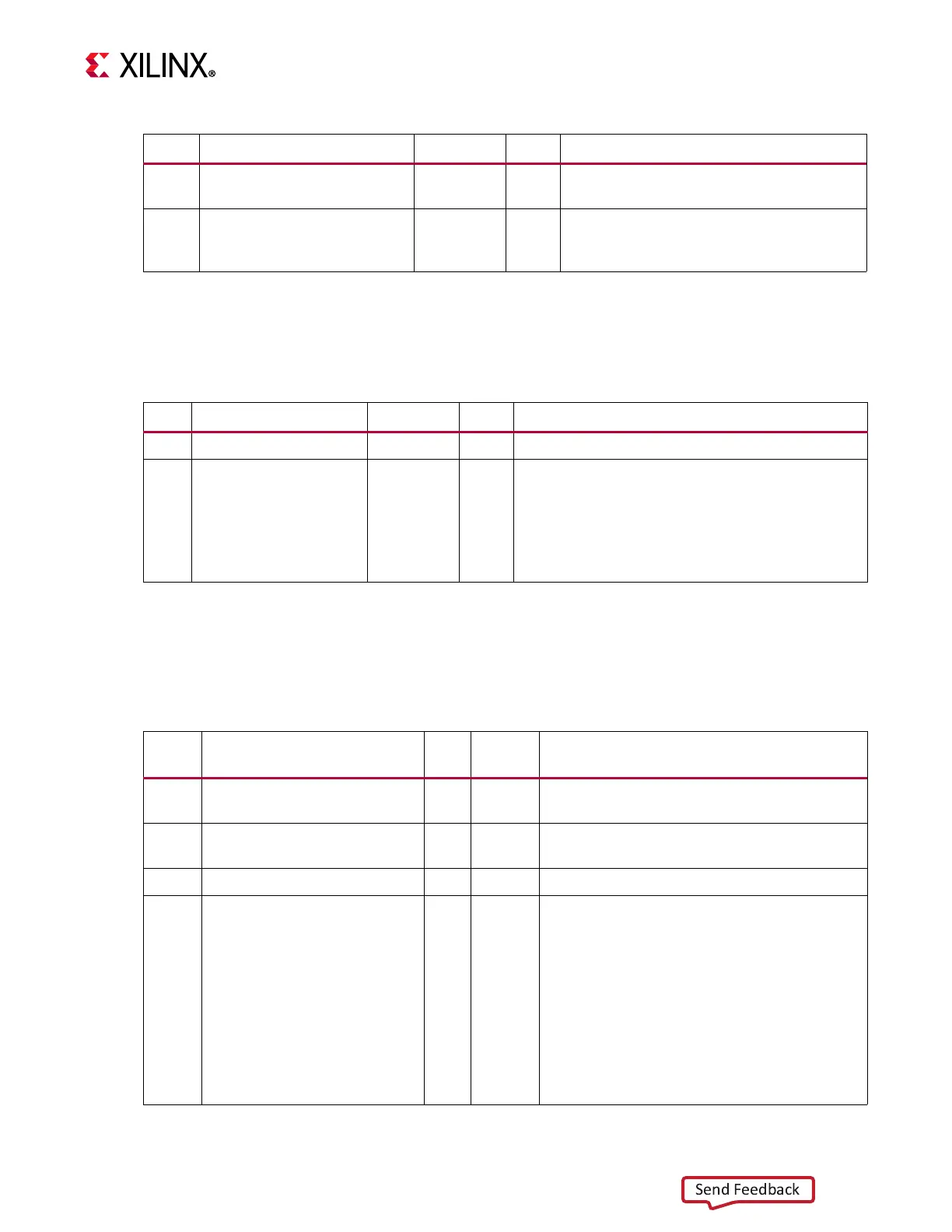

Table 2-11: Global Interrupt Enable Register (0x20)

Bits Name Reset Value Access Description

31–1 Reserved N/A N/A Reserved

0 Global Interrupt enable 0x0 R/W

Master enable for the device interrupt output to

the system

1: Enabled—the corresponding Interrupt Enable

register (IER) bits are used to generate interrupts

0: Disabled—Interrupt generation blocked

irrespective of IER bits

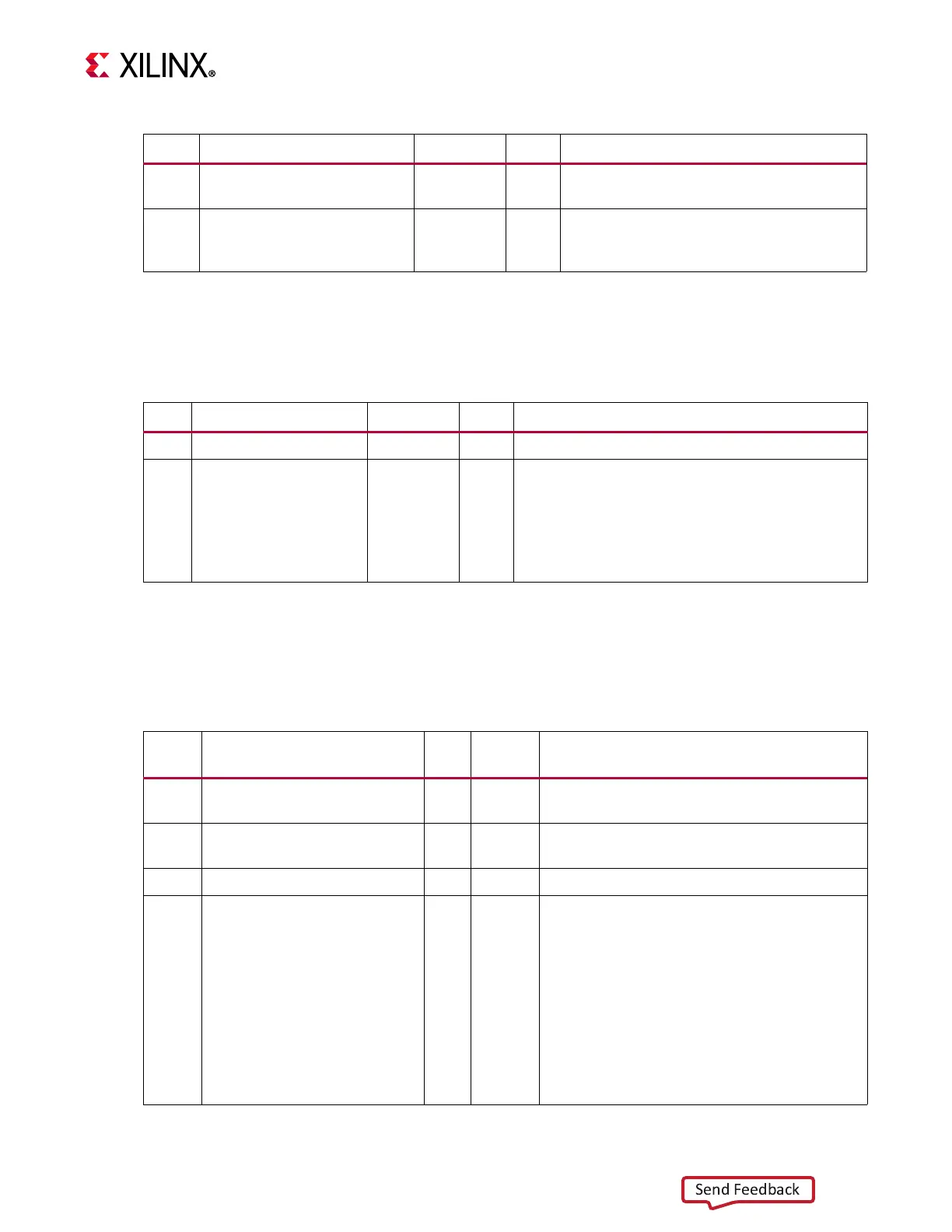

Table 2-12: Interrupt Status Register (0x24)

Bits Name

Reset

Value

Access

(1)

Description

31 Frame Received 0x0 R/W1C

Asserted when the Frame End (FE) short

packet is received for the current frame

30 VCX Frame Error RO 0x0

Asserted when the VCX Frame error is

detected

30–23 Reserved N/A N/A N/A

22 Word Count (WC) corruption 0x0 R/W1C

Asserted when WC field of packet header

corrupted and core receives less bytes than

indicated in WC field. Such a case can occur

only where more than 2-bits of header are

corrupted which ECC algorithm cannot report

and the corruption is such that the ECC

algorithm reports a higher Word Count (WC)

value as part of ECC correction.

In such case core limits processing of the

packet on reduced number of bytes received

through PPI interface.

Table 2-10: Core Status Register (0x10) (Cont’d)

Bits Name Reset Value Access Description

Loading...

Loading...