MIPI CSI-2 RX Subsystem v4.0 5

PG232 July 02, 2019 www.xilinx.com

Chapter 1

Overview

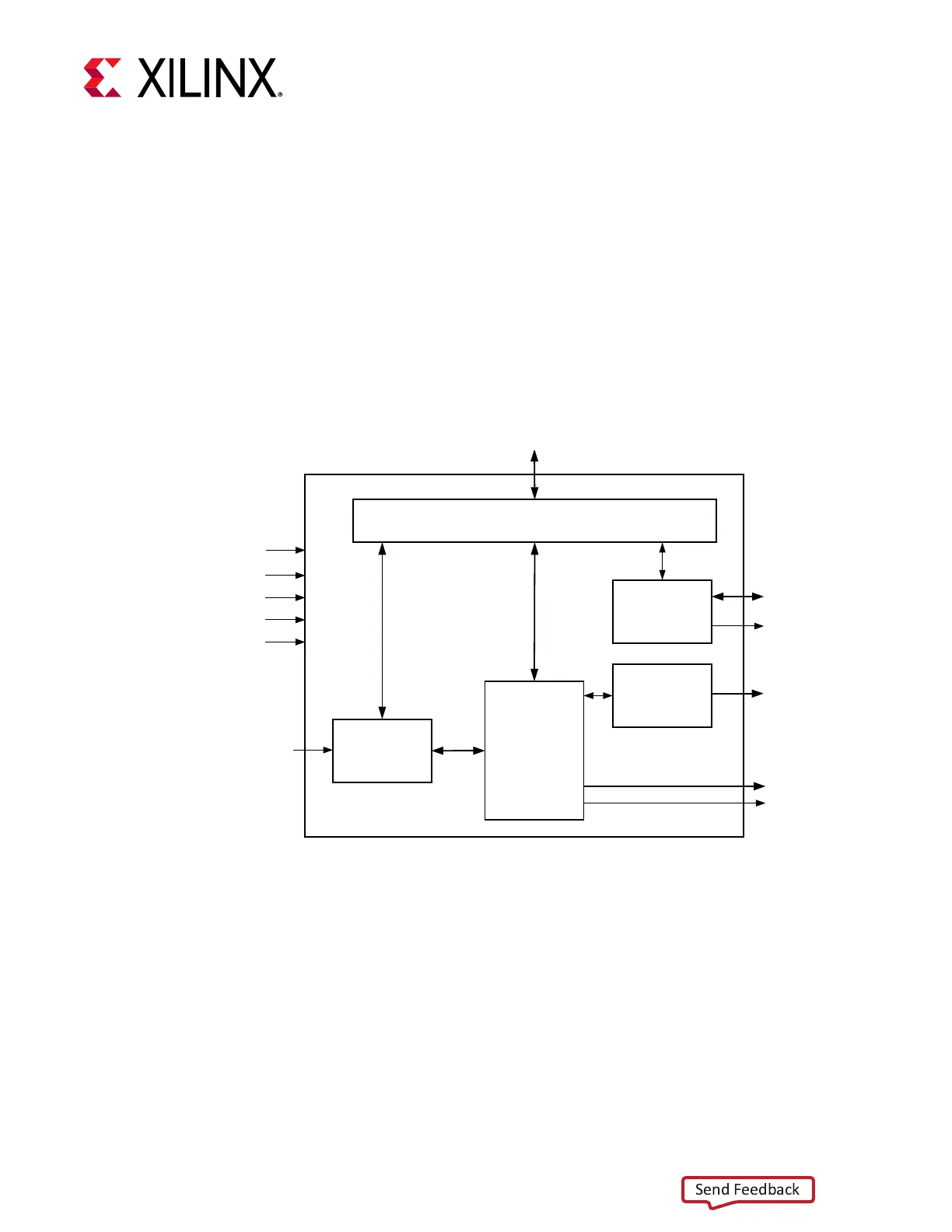

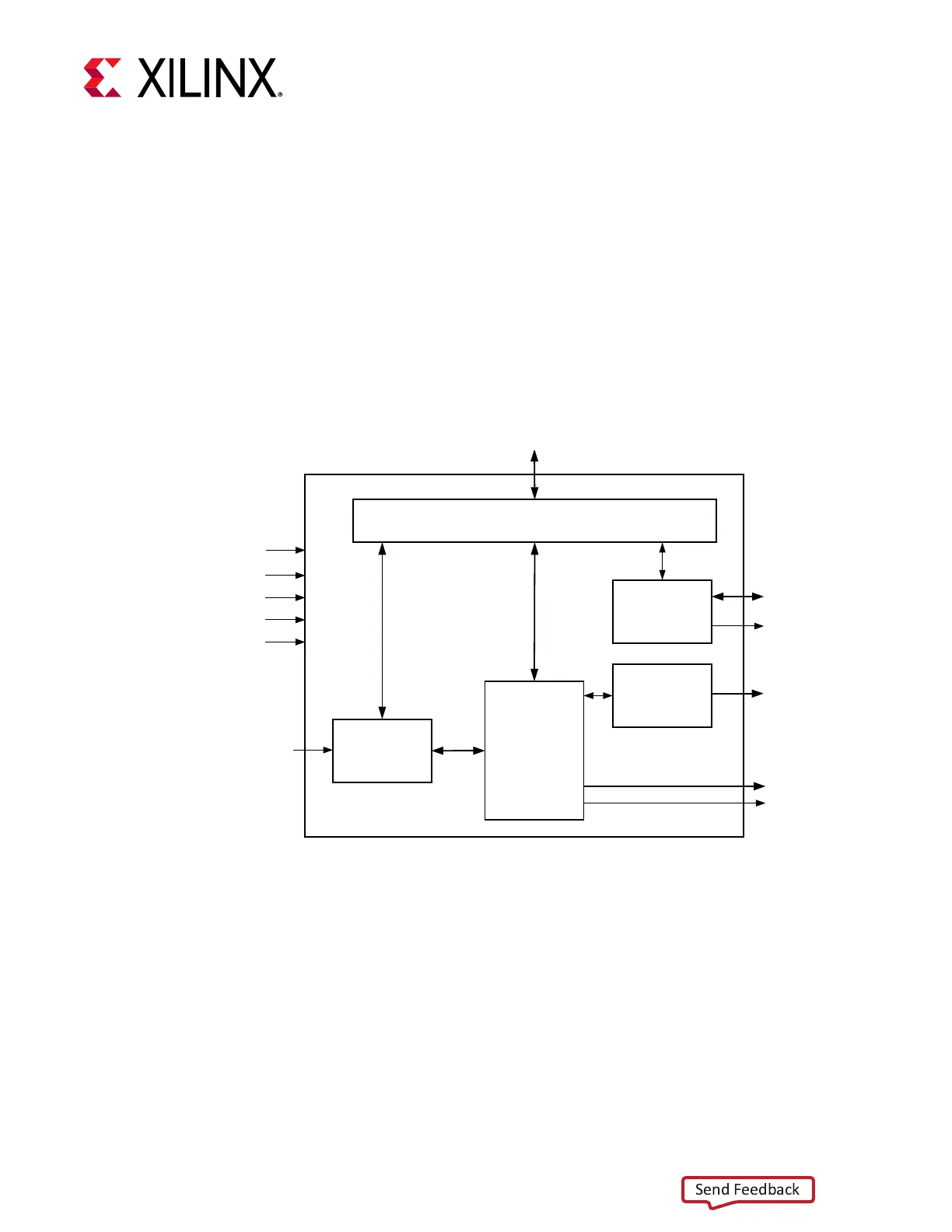

The MIPI CSI-2 RX subsystem allows you to quickly create systems based on the MIPI

protocol. It interfaces between MIPI-based image sensors and an image sensor pipe. An

internal high speed physical layer design, D-PHY, is provided that allows direct connection

to image sources. The top level customization parameters select the required hardware

blocks needed to build the subsystem. Figure 1-1 shows the subsystem architecture.

The subsystem consists of the following sub-cores:

•MIPI D-PHY

• MIPI CSI-2 RX Controller

• AXI CrossbarVideo Format Bridge

•AXI IIC

X-Ref Target - Figure 1-1

Figure 1-1: Subsystem Architecture

AXI Crossbar

AXI IIC

Video

Format

Bridge

MIPI CSI-2 RX

Controller

MIPI D-PHY

Video Interface

(AXI4-Stream)

Embedded Non-Image

Interface (AXI4-Stream)

csirxss_csi_irq

csirxss_iic_irq

Serial Interface

AXI4-Lite Interface

IIC Interface

PPI

dphy_clk_200M

lite_aclk

lite_aresetn

video_aclk

video_aresetn

Loading...

Loading...