MIPI CSI-2 RX Subsystem v4.0 8

PG232 July 02, 2019 www.xilinx.com

Chapter 1: Overview

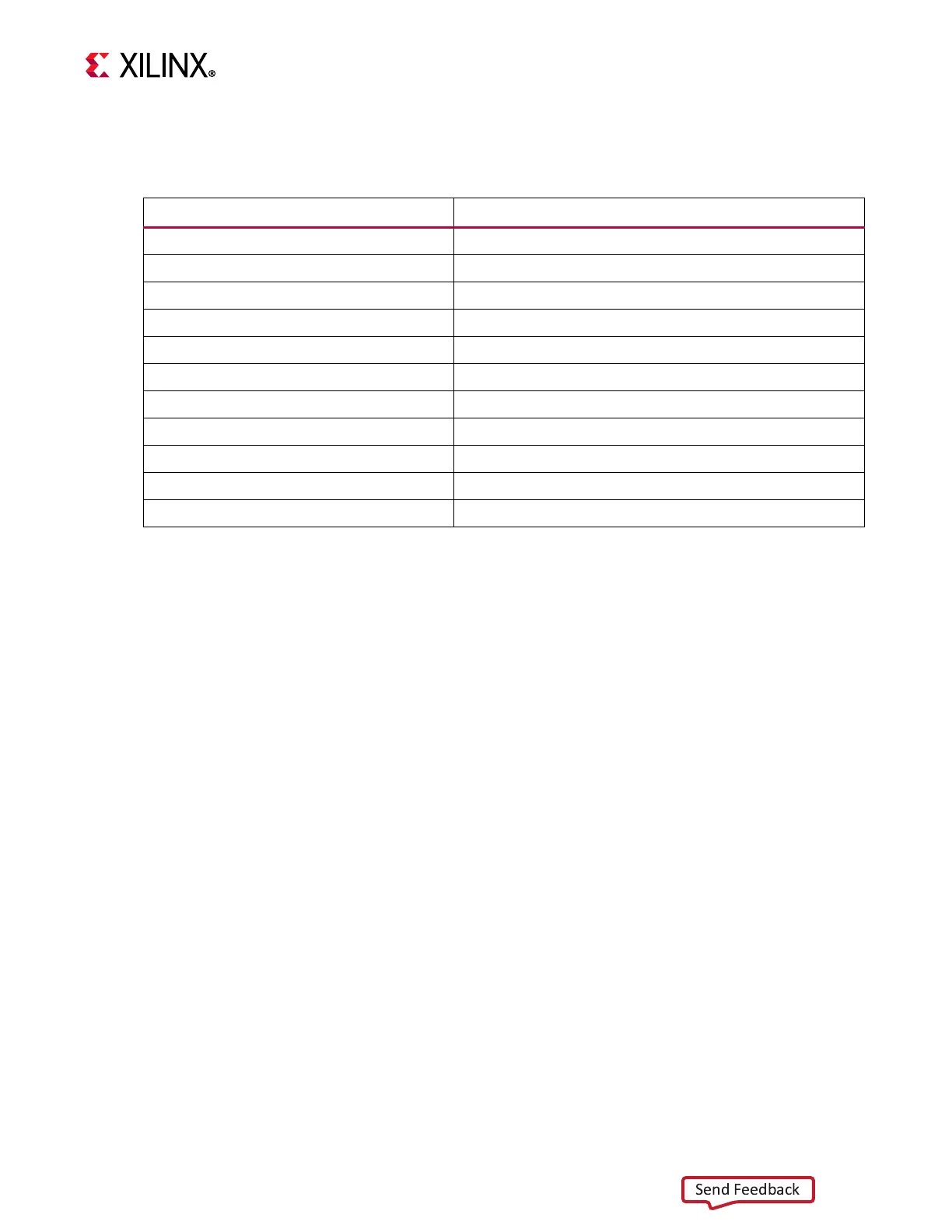

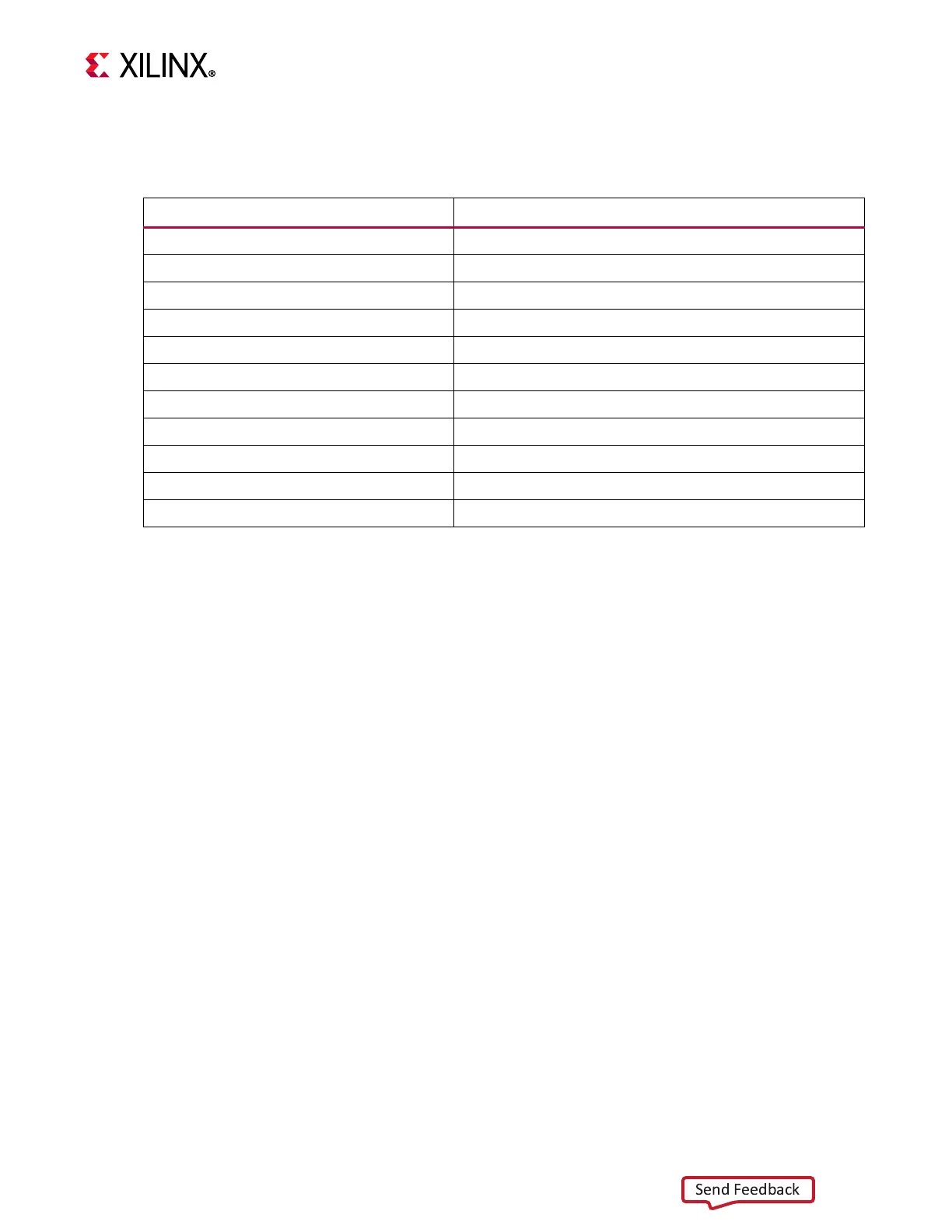

As shown in Tabl e 1- 1 the embedded non-image (with data type code 0x12) AXI4-Stream

interface data width is selected based on the Data Type selected.

Abrupt termination events such as a soft reset, disabling a core while a packet is being

written to the line buffer, or a line buffer full condition results in early termination. The

termination is implemented by assertion of EOL on the video interface or TLAST and

TUSER[1] on the embedded non-image interface, based on the current long packet being

processed.

ECC/CRC Forwarding

Sideband signals of AXI4-Stream interface [Include/Exclude Video Format Bridge and

Embedded non-image interface] report ECC and CRC data received from the source [sensor]

to downstream IPs. This allows to re-calculate ECC/CRC by the downstream IPs in certain

functional safety applications. See Port Descriptions for details on signal mapping.

In error scenarios like abrupt termination due to soft reset, disabling the core while packet

transfer in progress, line buffer in full condition, word count of received packet is greater

than the actual payload, these sideband signals do not report the correct ECC and CRC.

VCX Support

The MIPI CSI-2 standard v2.0 specific VCX support feature is used to extend the maximum

number of available virtual channels to 16. When this feature is enabled, the virtual channel

is deduced by combining the 2-bit VC field (LSB) and the 2-bit VCX field (MSB) from the

packet header.

Table 1-1: Embedded Non-Image AXI4-Stream Interface TDATA Widths

Data Type (DT) AXI4-Stream Interface TDATA Width

RAW6 32

RAW7 32

RAW8 32

RAW10 64

RAW12 64

RAW14 64

RAW16 64

RAW20 64

All RGB 64

YUV 422 8–bit 64

YUV 422 10–bit 64

Loading...

Loading...