MIPI CSI-2 RX Subsystem v4.0 85

PG232 July 02, 2019 www.xilinx.com

Appendix B: Debugging

AXI4-Stream Interfaces

If data is not being transmitted or received, check the following conditions:

•If transmit <interface_name>_tready is stuck Low following the

<interface_name>_tvalid input being asserted, the subsystem cannot send data.

•If the receive <interface_name>_tvalid is stuck Low, the subsystem is not

receiving data.

• Check that the video_aclk and dphy_clk_200M inputs are connected and toggling.

• Check subsystem configuration.

• Ensure “Stream line buffer full” condition not getting reported in subsystem Interrupt

Status register.

Sideband Information on AXI4-Stream Interfaces

• Sideband information such as frame and line number appear on the TUSER signal of

the AXI4-Stream interface.

• Start of fame, frame number, line number, word count, and data type need to be

sampled by the user on the first beat of the transfer.

• Packet Error, ECC, and CRC need to be sampled by the user on the last beat of the

transfer.

Note:

The side band information are optionally sent by the sensor. Please refer to the Low Level

Protocol section of MIPI CSI-2 standard v2.0 [Ref 1] for more details.

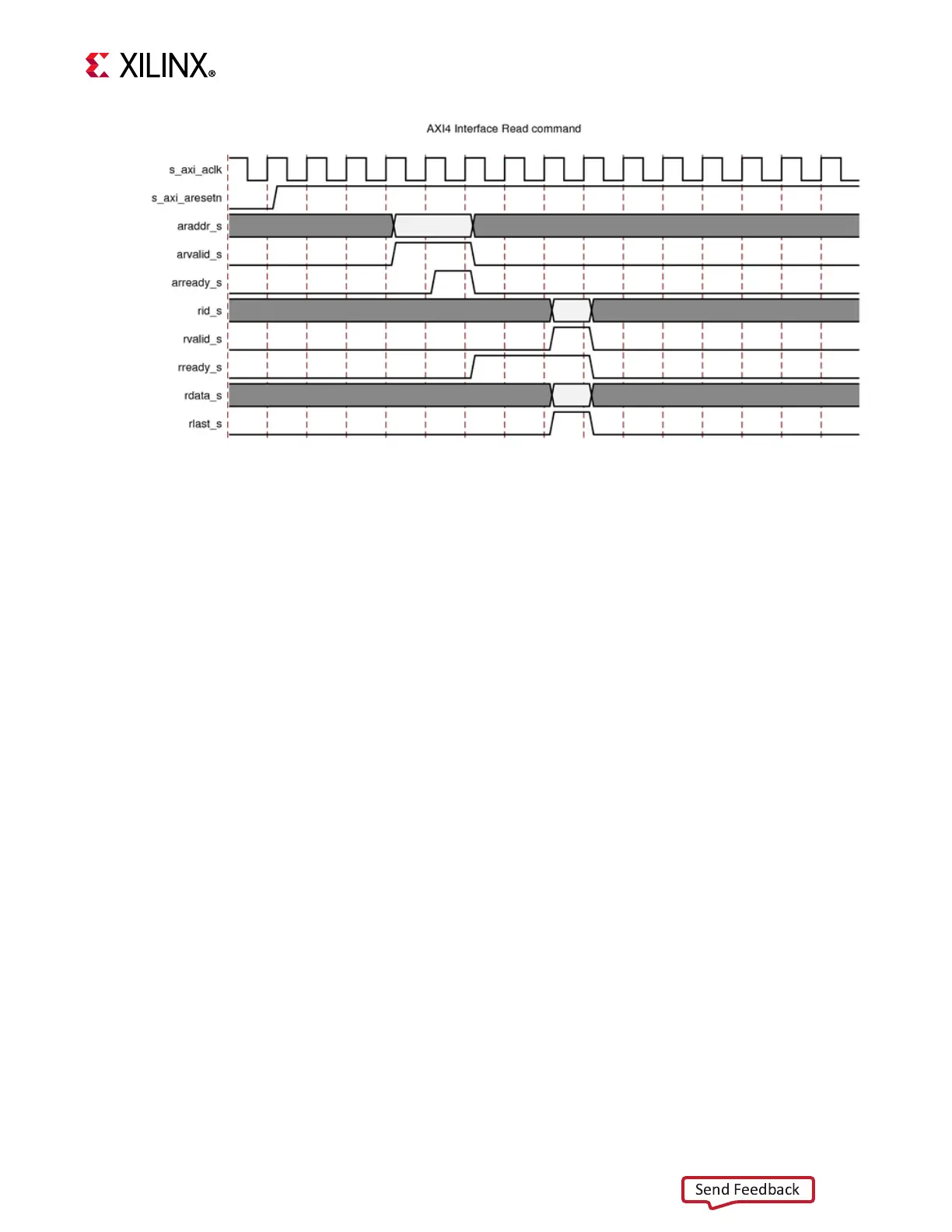

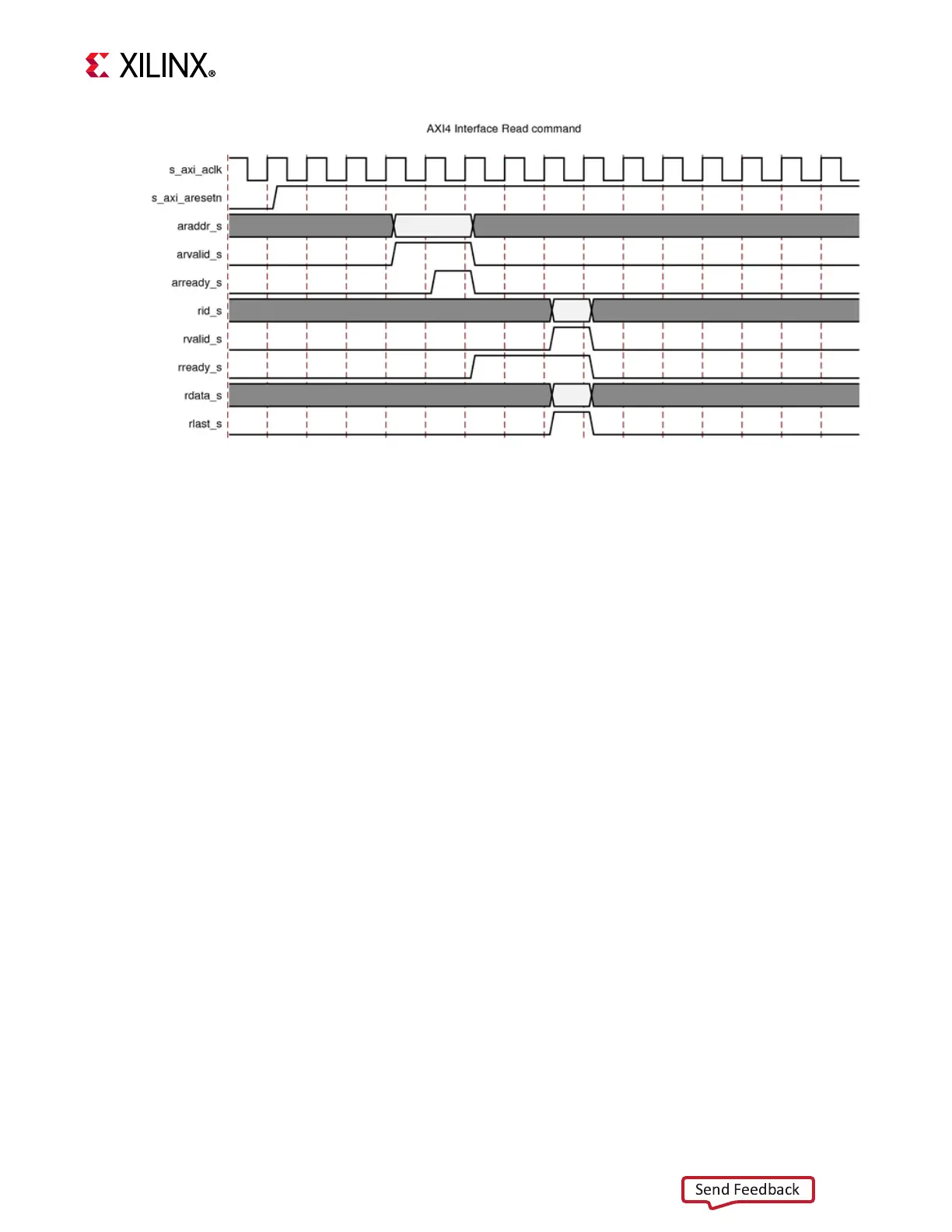

X-Ref Target - Figure B-1

Figure B-1: AXI4-Lite Timing

Loading...

Loading...