MIPI CSI-2 RX Subsystem v4.0 29

PG232 July 02, 2019 www.xilinx.com

Chapter 2: Product Specification

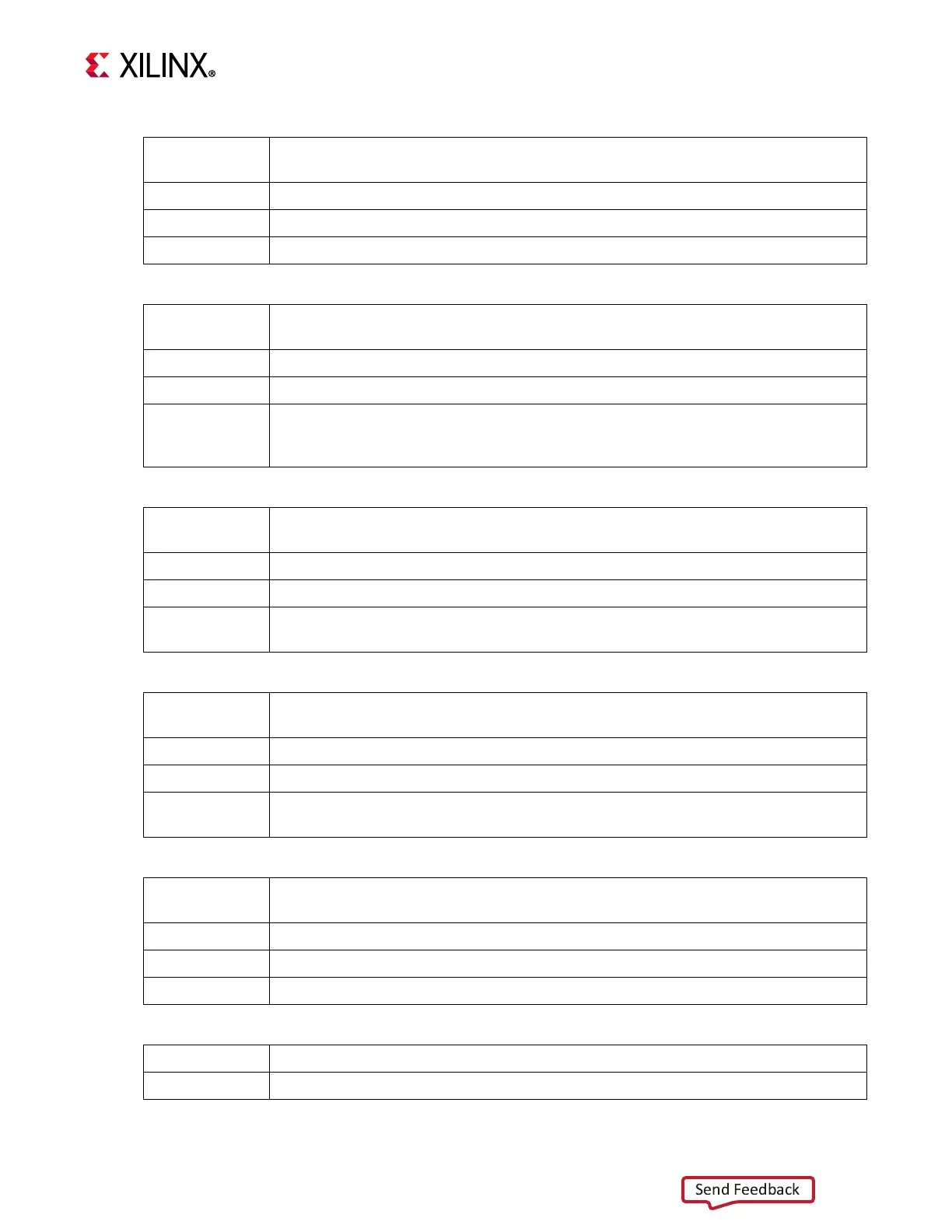

Table 2-15: Control Error, Escape Entry Error, Escape Ultra Low Power Mode, Stopstate

Set Condition(s)

Set by the core when the condition for the corresponding signal as defined in the

MIPI CSI-2 specification [Ref 1] is seen, reported through the PPI interface.

Reset Sequence Write 1 to clear this bit.

Priority Set condition takes priority over reset sequence.

Impact Current packet being processed does not have any impact.

Table 2-16: SoT Error

Set Condition(s)

Set by the core when the current packet being processed has Start-of-Transmission

(SoT) Error reported through PPI Interface.

Reset Sequence Write 1 to clear this bit.

Priority Set condition takes priority over reset sequence.

Impact

Current packet under process does not have any impact as synchronization is still

achieved. This is considered to be a “soft error” in the leader sequence and

confidence in the payload data is reduced.

Table 2-17: SoT Sync Error

Set Condition(s)

Set by the core when current packet being processed has Start-of-Transmission

Synchronization Error reported through PPI interface.

Reset Sequence Write 1 to clear this bit.

Priority Set condition takes priority over reset sequence.

Impact

The current packet being processed is not processed further. The core waits for the

next packet to process.

Table 2-18: ECC 2-Bit Error

Set Condition(s)

Set by the core when an ECC syndrome was computed and two bit-errors are detected

in the received Packet Header.

Reset Sequence Write 1 to clear this bit.

Priority Set condition takes priority over reset sequence.

Impact

Current packet being processed is not processed further as WC is not usable, and thus

the packet end cannot be estimated.The core waits for the next packet to process.

Table 2-19: ECC 1-Bit Error

Set Condition(s)

Set by the core when an ECC syndrome was computed and a single bit-error in the

Packet Header was detected and corrected.

Reset Sequence Write 1 to clear this bit.

Priority Set condition takes priority over reset sequence.

Impact Current packet being processed does not have any impact.

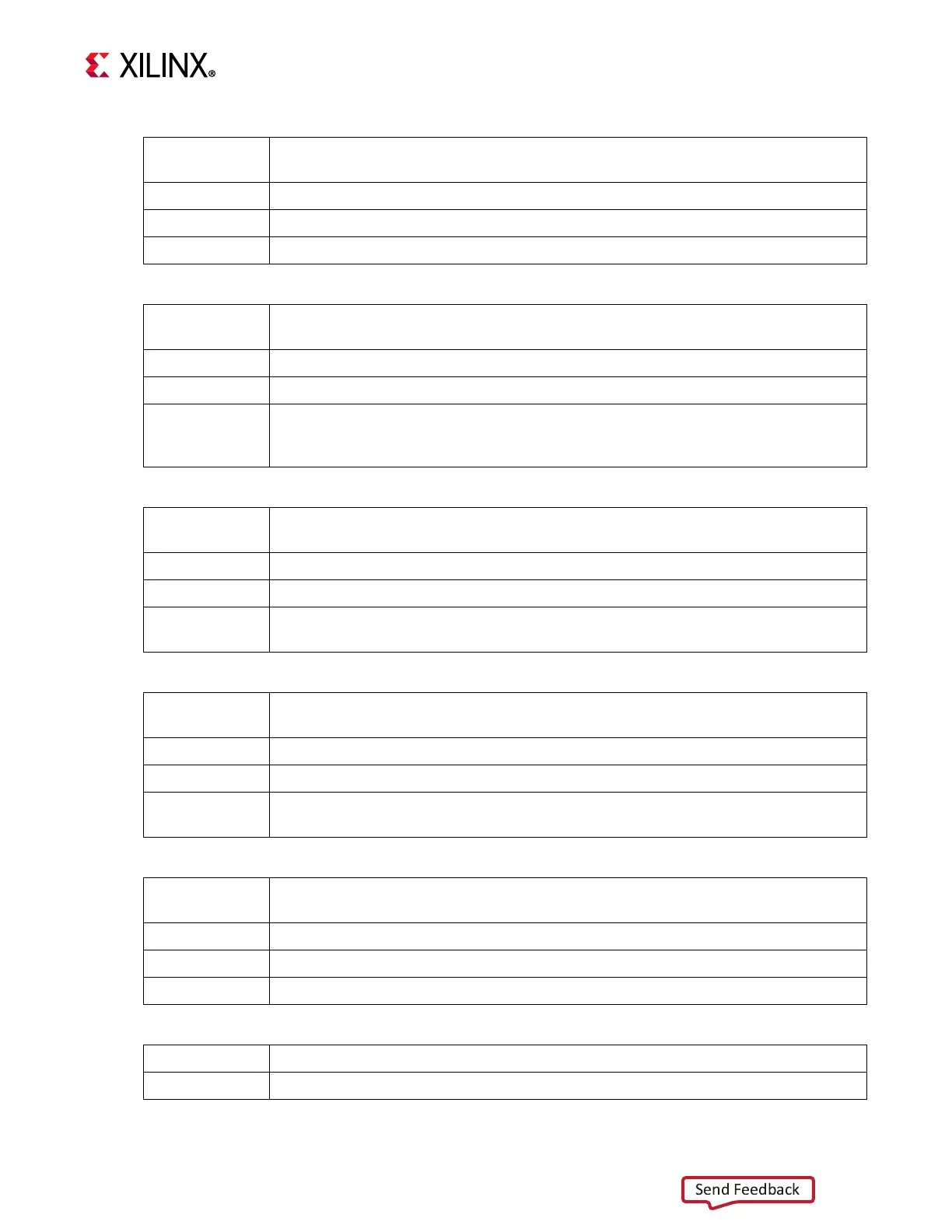

Table 2-20: CRC Error

Set Condition(s) Set by the core when the computed CRC code is different than the received CRC code.

Reset Sequence Write 1 to clear this bit.

Loading...

Loading...