MIPI CSI-2 RX Subsystem v4.0 25

PG232 July 02, 2019 www.xilinx.com

Chapter 2: Product Specification

Protocol Configuration Register

The Protocol Configuration register is described in Ta b l e 2-9 and allows you to configure

protocol specific options such as the number of lanes to be used.

Core Status Register

The Core Status register is described in Ta ble 2-1 0 .

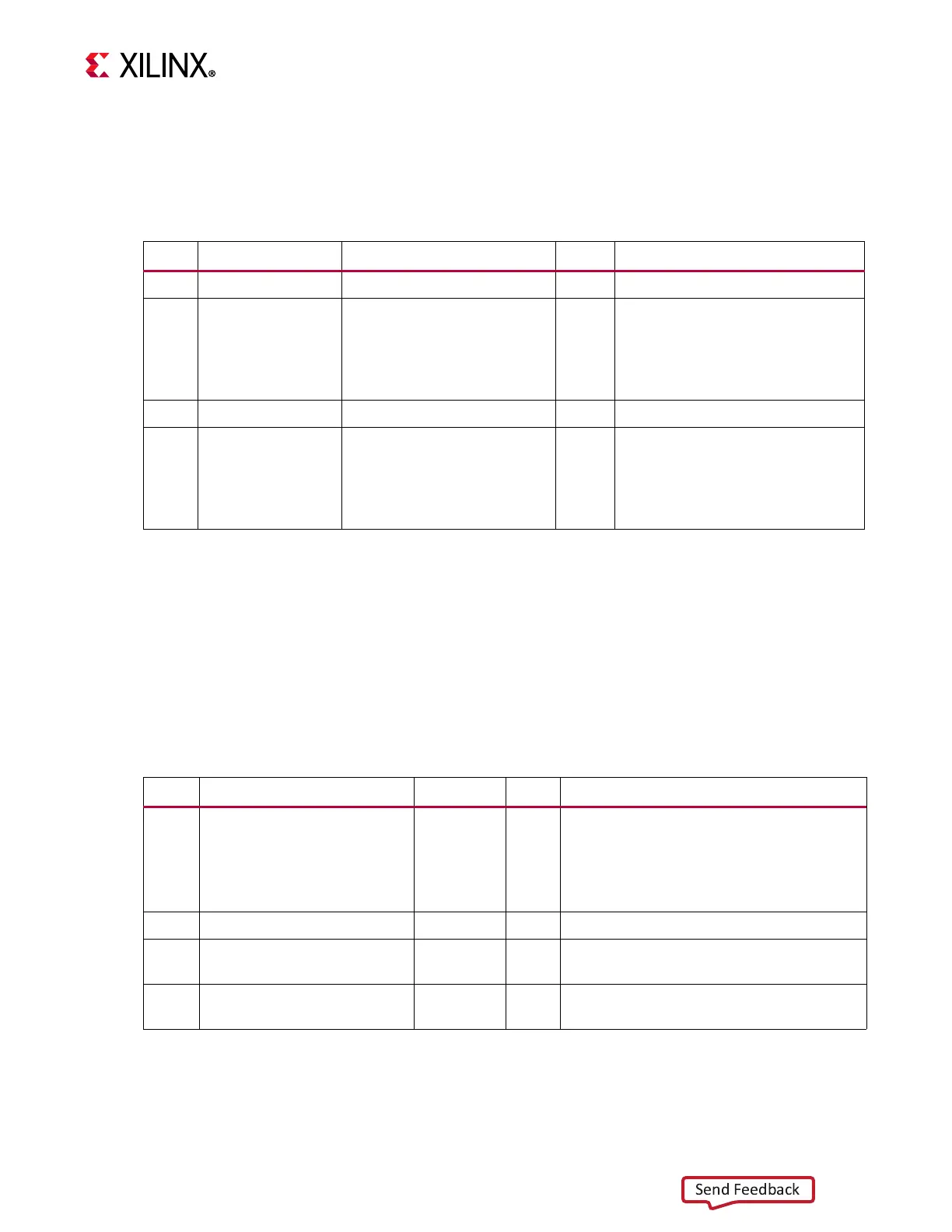

Table 2-9: Protocol Configuration Register (0x04)

Bits Name Reset Value Access Description

31–5 Reserved N/A N/A Reserved

4–3 Maximum Lanes

(1)

Number of lanes configured

during core generation

R

Maximum lanes of the core

0x0—1 Lane

0x1—2 Lanes

0x2—3 Lanes

0x3—4 Lanes

2 Reserved N/A Reserved

1–0 Active Lanes

Number of lanes configured

during core generation

R

(2)

/W

Active lanes in the core

(3)

0x0—1 Lane

0x1—2 Lanes

0x2 —3 Lanes

0x3—4 Lanes

Notes:

1. Maximum Lanes cannot exceed the number of lanes as set by the Serial Data Lanes parameter at generation time.

2. A read from this register reflects the current number of lanes being used by core. This is useful when dynamically

updating the active lanes during core operation to ensure that the core is using the new active lanes information.

See Chapter 3, Designing with the Subsystem for more information.

3. Active Lanes cannot exceed the Maximum Lanes as set in the Protocol Configuration register setting of bits 4–3.

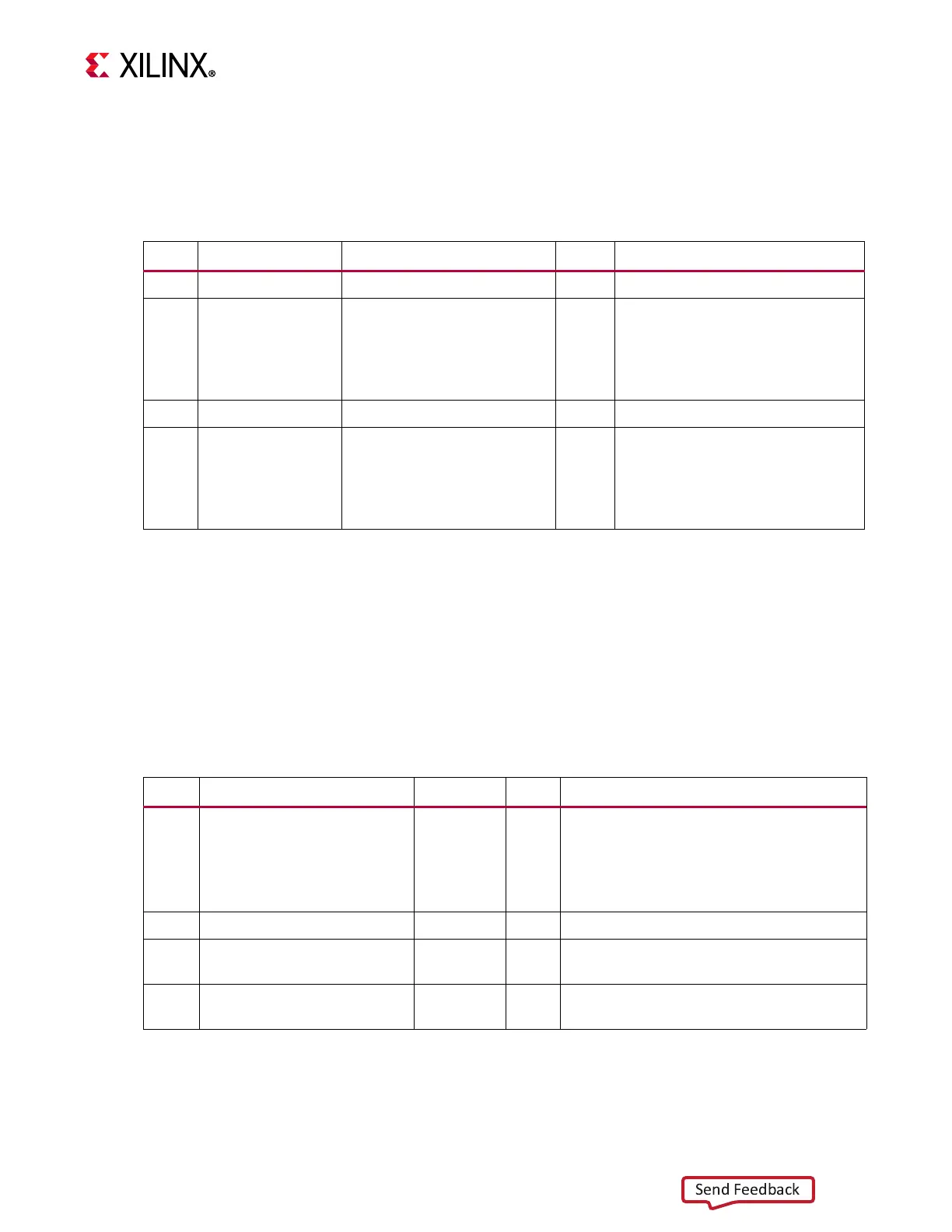

Table 2-10: Core Status Register (0x10)

Bits Name Reset Value Access Description

31–16 Packet Count 0x0 R

Counts number of long packets written to

the line buffer

• No roll-over of this counter reported/

supported

• Count includes error packets (if any)

15–4 Reserved N/A N/A N/A

3 Short packet FIFO Full 0x0 R

Indicates the current status of short packet

FIFO full condition

2 Short packet FIFO not empty 0x0 R

FIFO not empty: Indicates the current status

of short packet FIFO not empty condition

Loading...

Loading...