MIPI CSI-2 RX Subsystem v4.0 32

PG232 July 02, 2019 www.xilinx.com

Chapter 2: Product Specification

Generic Short Packet Register

The Generic Short Packet register is described in Tab l e 2 - 26. Packets received with generic

short packet codes are stored in a 31-deep internal FIFO and are made available through

this register. The following conditions reset the FIFO:

•External reset on video_aresetn

• Core disable or soft reset through register settings.

VCX Frame Error Register

The VCX Frame Error register is described in Table. It captures the frame level and frame

synchronization errors for the VC extension channels.

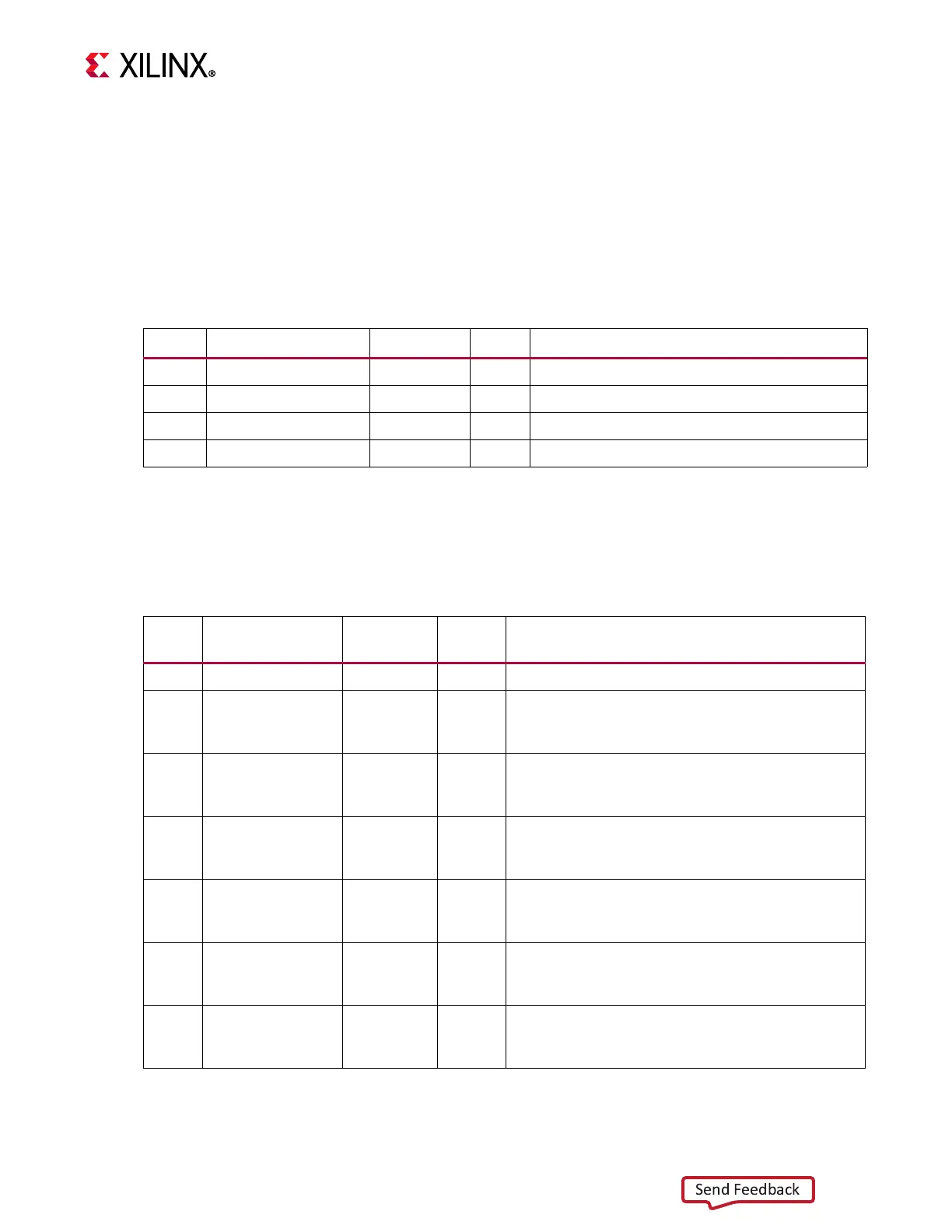

Table 2-26: Generic Short Packet Register (0x30)

Bits Name Reset Value Access Description

31–24 Reserved N/A N/A Reserved

23–8 Data 0x0 R 16-bit short packet data

7–6 Virtual Channel 0x0 R Virtual channel number

5–0 Data Type 0x0 R Generic short packet code

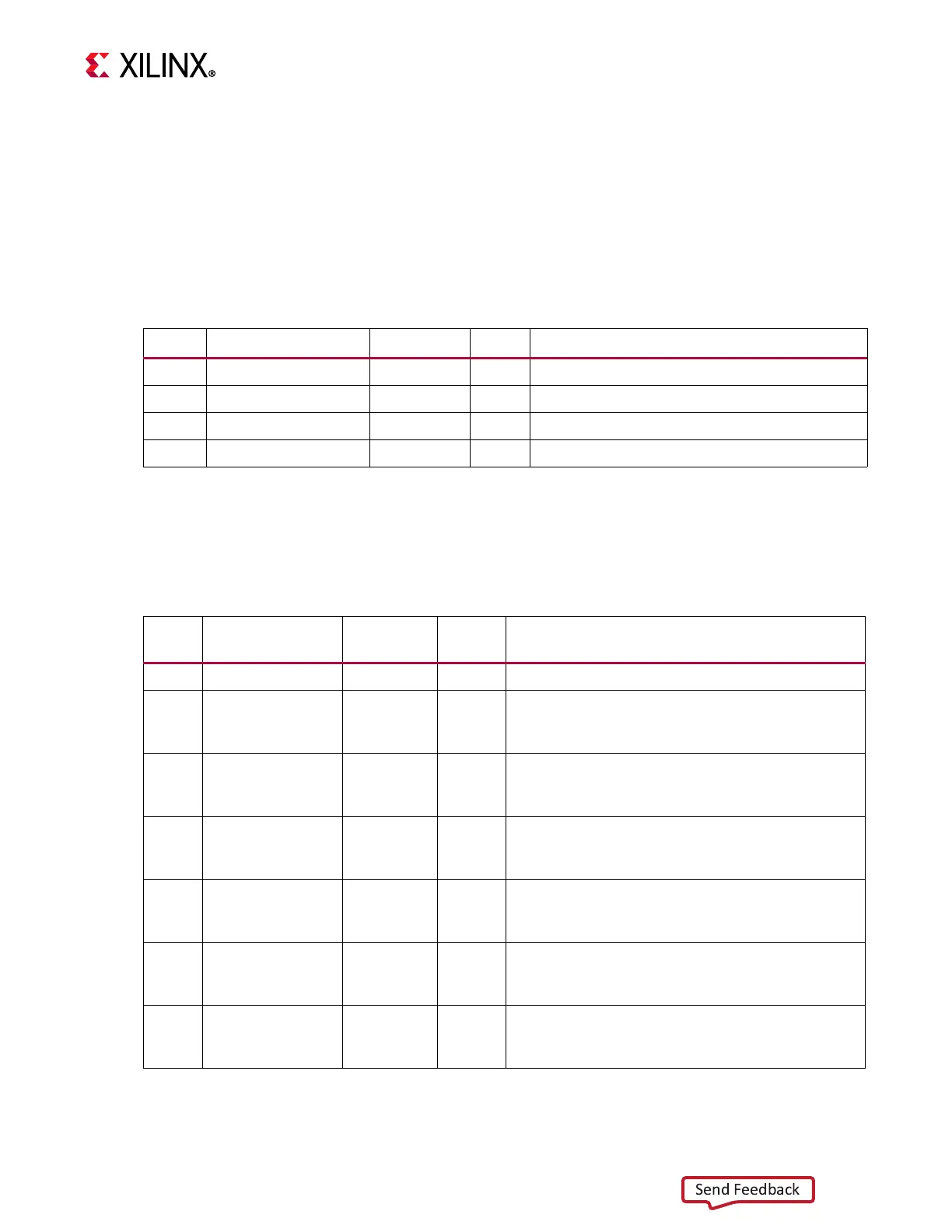

Table 2-27: VCX Frame Error (0x34)

Bits Name Access

Default

Value

Description

31–24 Reserved N/A N/A Reserved

23 Frame

synchronization

error for VC15

R/W1C 0x0 Asserted when an FE is not paired with a Frame

Start (FS) on the same virtual channel.

22 Frame level error

for VC15

R/W1C 0x0 Asserted after an FE when the data payload

received between FS and FE contains errors. The

data payload errors are CRC errors.

21 Frame

synchronization

error for VC14

R/W1C 0x0 Asserted when an FE is not paired with a Frame

Start (FS) on the same virtual channel.

20 Frame level error

for VC14

R/W1C 0x0 Asserted after an FE when the data payload

received between FS and FE contains errors. The

data payload errors are CRC errors.

19 Frame

synchronization

error for VC13

R/W1C 0x0 Asserted when an FE is not paired with a Frame

Start (FS) on the same virtual channel.

18 Frame level error

for VC13

R/W1C 0x0 Asserted after an FE when the data payload

received between FS and FE contains errors. The

data payload errors are CRC errors.

Loading...

Loading...