MIPI CSI-2 RX Subsystem v4.0 21

PG232 July 02, 2019 www.xilinx.com

Chapter 2: Product Specification

Register Space

This section details registers available in the MIPI CSI-2 RX Subsystem. The address map is

split into following regions:

• MIPI CSI-2 RX Controller core

•AXI IIC core

•MIPI D-PHY core

Each IP core is given an address space of 64K. Example offset addresses from the system

base address when the AXI IIC and MIPI D-PHY registers are enabled are shown in Tabl e 2- 6 .

MIPI CSI-2 RX Controller Core Registers

Tab l e 2 - 7 specifies the name, address, and description of each firmware addressable

register within the MIPI CSI-2 RX controller core.

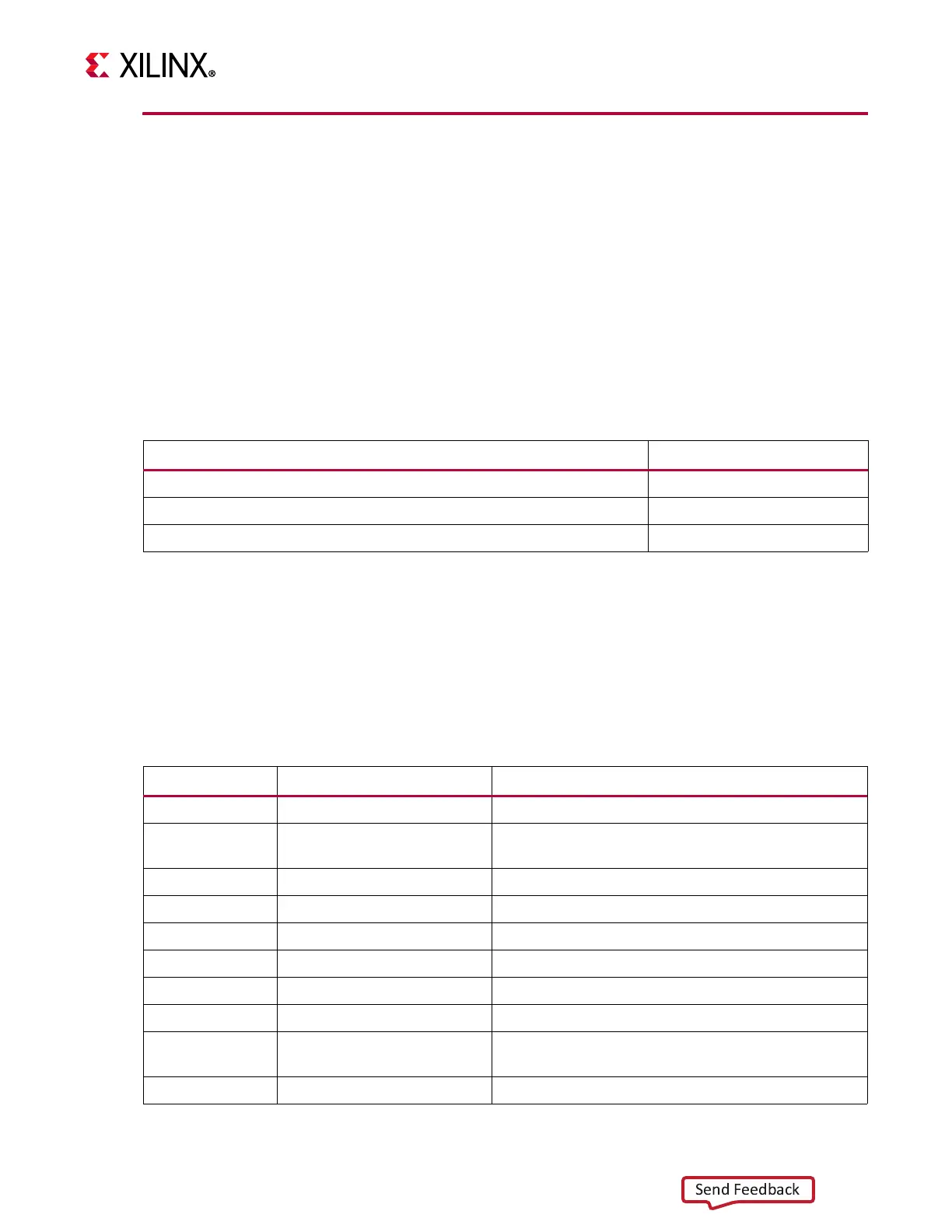

Table 2-6: Sub-Core Address Offsets

IP Cores Offset

MIPI CSI-2 RX Controller 0x0_0000

AXI IIC 0x1_0000

MIPI D-PHY 0x2_0000

(1)

Notes:

1. When the AXI IIC core is not present, the MIPI D-PHY offset moves up and starts at 0x1_0000. The software driver

handles this seamlessly.

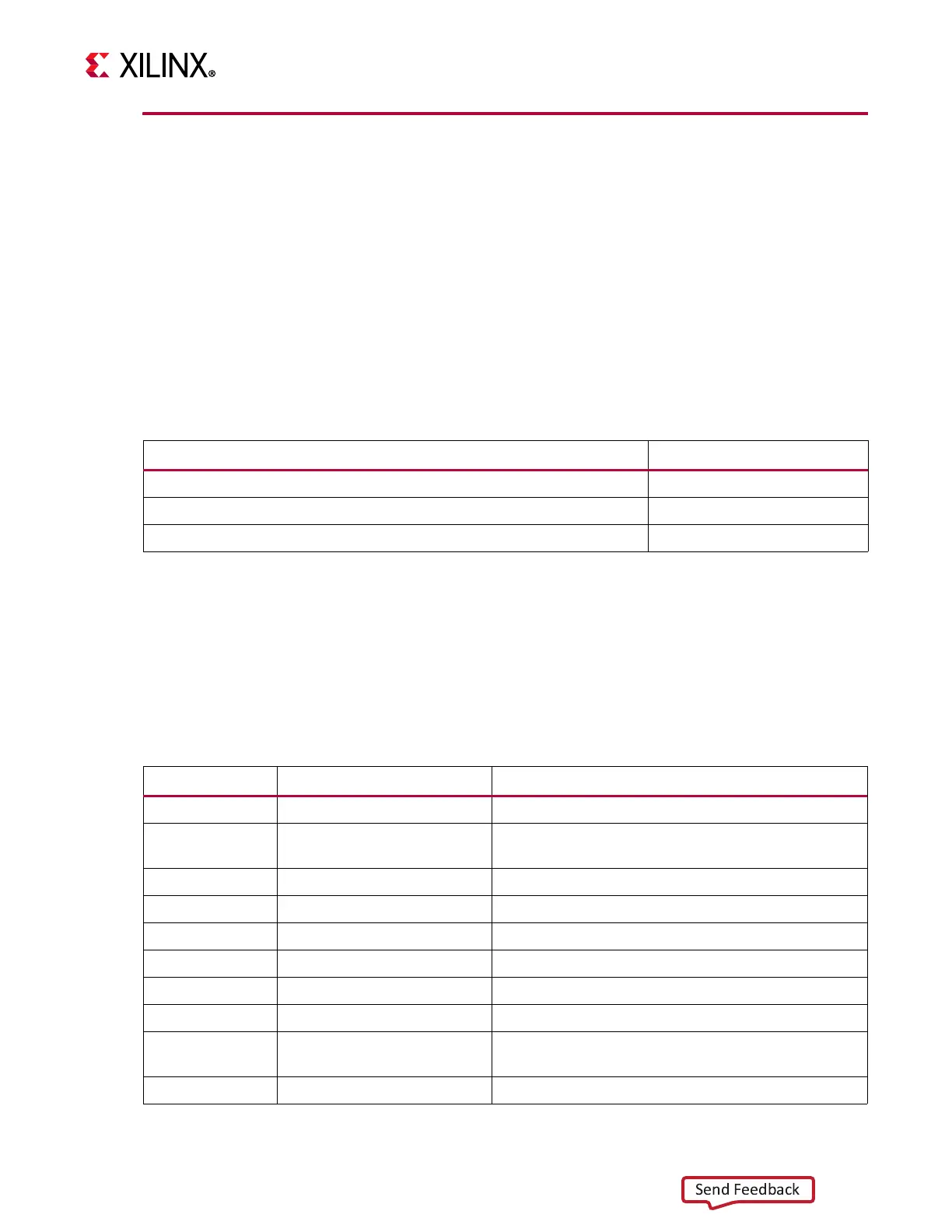

Table 2-7: MIPI CSI-2 RX Controller Core Registers

Address Offset Register Name Description

0x00 Core Configuration Register Core configuration options

0x04

Protocol Configuration

Register

Protocol configuration options

0x08 Reserved

(1)

0x0C Reserved

0x10 Core Status Register Internal status of the core

0x14 Reserved

0x18 Reserved

0x1C Reserved

0x20

Global Interrupt Enable

Register

Global interrupt enable registers

0x24 Interrupt Status Register Interrupt status register

Loading...

Loading...