MIPI CSI-2 RX Subsystem v4.0 22

PG232 July 02, 2019 www.xilinx.com

Chapter 2: Product Specification

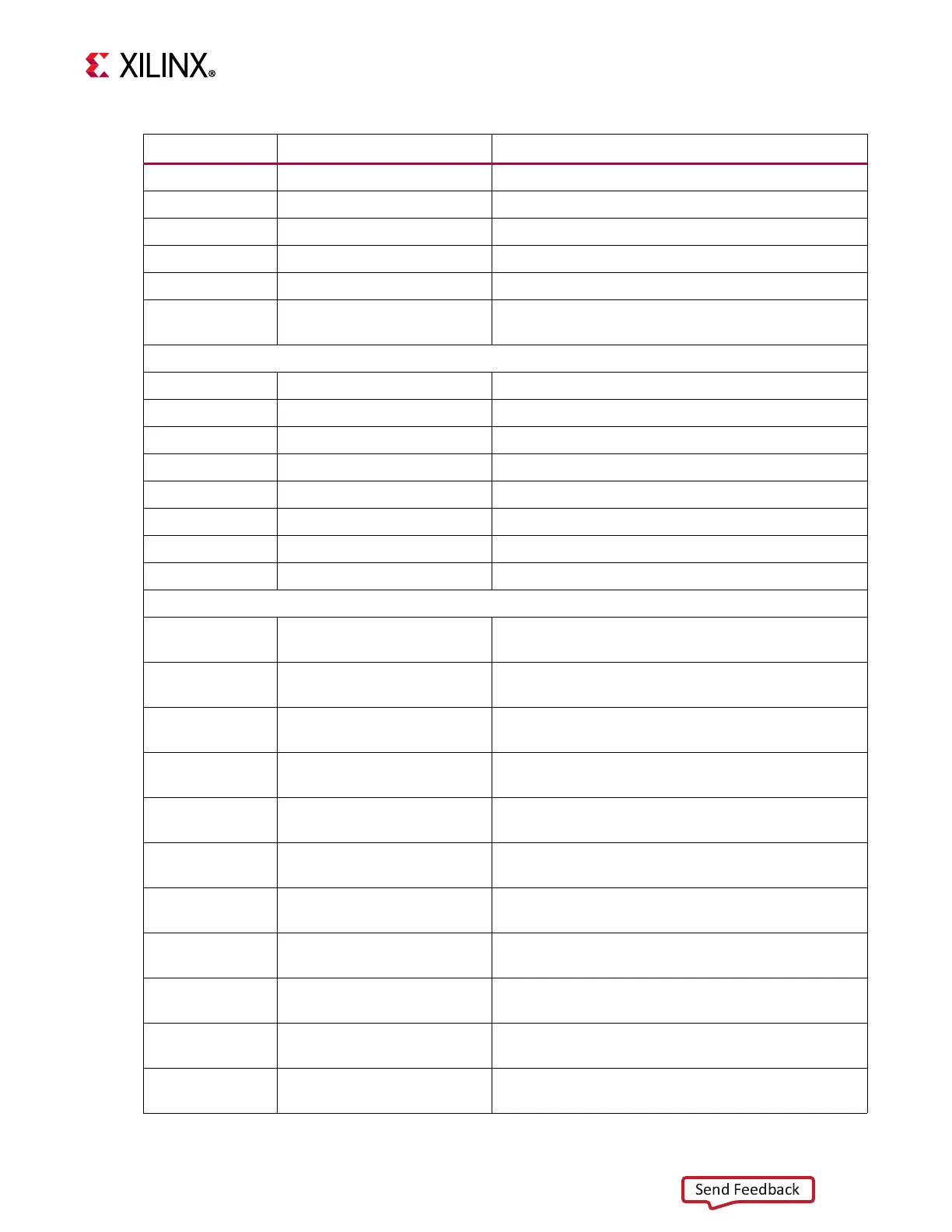

0x28 Interrupt Enable Register Interrupt enable register

0x2C Reserved

0x30 Generic Short Packet Register Short packet data

0x34 VCX Frame Error Register VCX Frame Error Register

0x38 Reserved

0x3C

Clock Lane Information

Register

Clock lane status information

Lane<n> Information Registers

0x40 Lane0 Information Lane 0 status information

0x44 Lane1 Information Lane 1 status information

0x48 Lane2 Information Lane 2 status information

0x4C Lane3 Information Lane 3 status information

0x50 Reserved

0x54 Reserved

0x58 Reserved

0x5C Reserved

Image Information 1 Registers (VC0 to VC15) and Image Information 2 Registers (VC0 to VC15)

0x60 Image Information 1 for VC0

Image information 1 of the current processing packet

with VC of 0

0x64 Image Information 2 for VC0

Image information 2 of the current processing packet

with VC of 0

0x68 Image Information 1 for VC1

Image information 1 of the current processing packet

with VC of 1

0x6C Image Information 2 for VC1

Image information 2 of the current processing packet

with VC of 1

0x70 Image Information 1 for VC2

Image information 1 of the current processing packet

with VC of 2

0x74 Image Information 2 for VC2

Image information 2 of the current processing packet

with VC of 2

0x78 Image Information 1 for VC3

Image information 1 of the current processing packet

with VC of 3

0x7C Image Information 2 for VC3

Image information 2 of the current processing packet

with VC of 3

0x80 Image Information 1 for VC4

Image information 1 of the current processing packet

with VC of 4

0x84 Image Information 2 for VC4

Image information 2 of the current processing packet

with VC of 4

0x88 Image Information 1 for VC5

Image information 1 of the current processing packet

with VC of 5

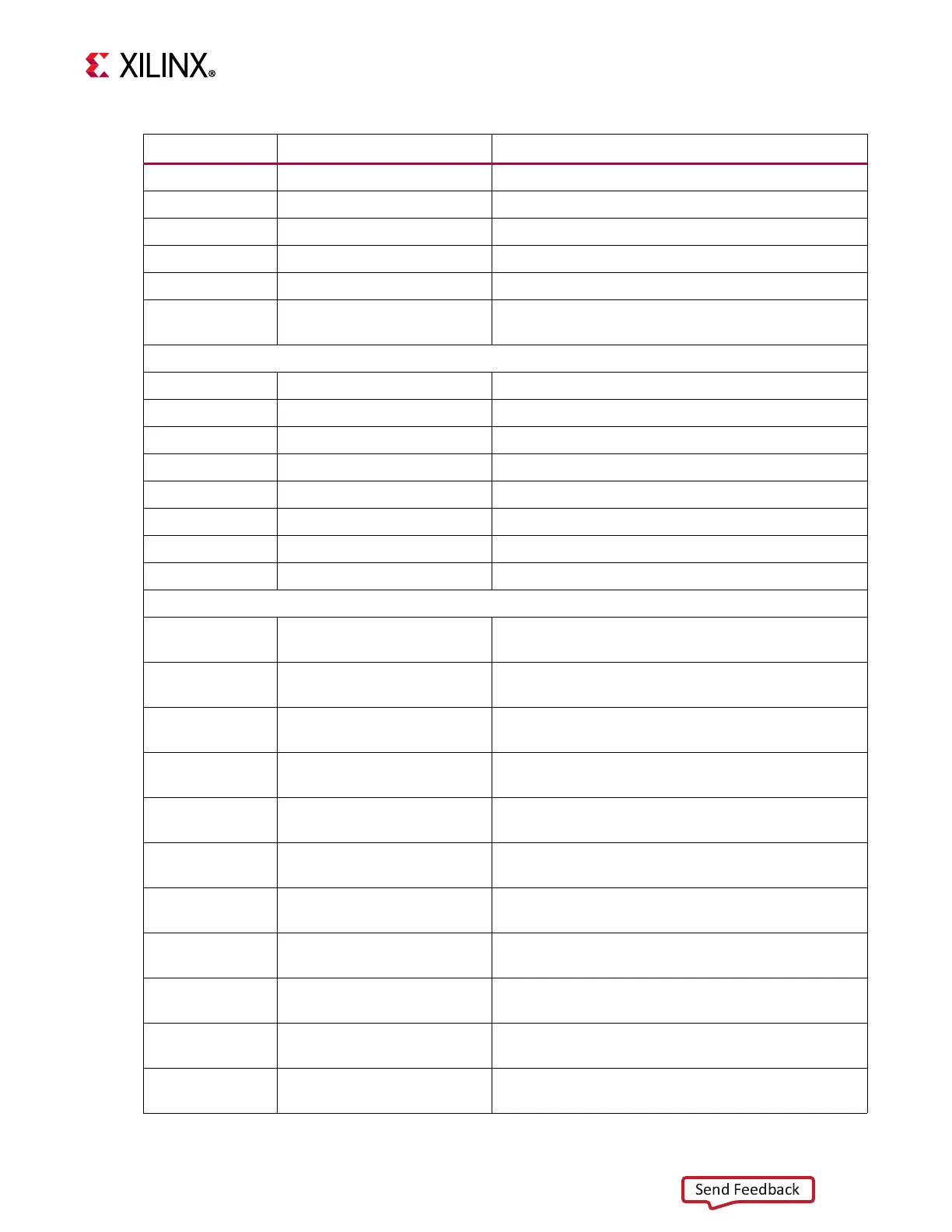

Table 2-7: MIPI CSI-2 RX Controller Core Registers (Cont’d)

Address Offset Register Name Description

Loading...

Loading...