MIPI CSI-2 RX Subsystem v4.0 23

PG232 July 02, 2019 www.xilinx.com

Chapter 2: Product Specification

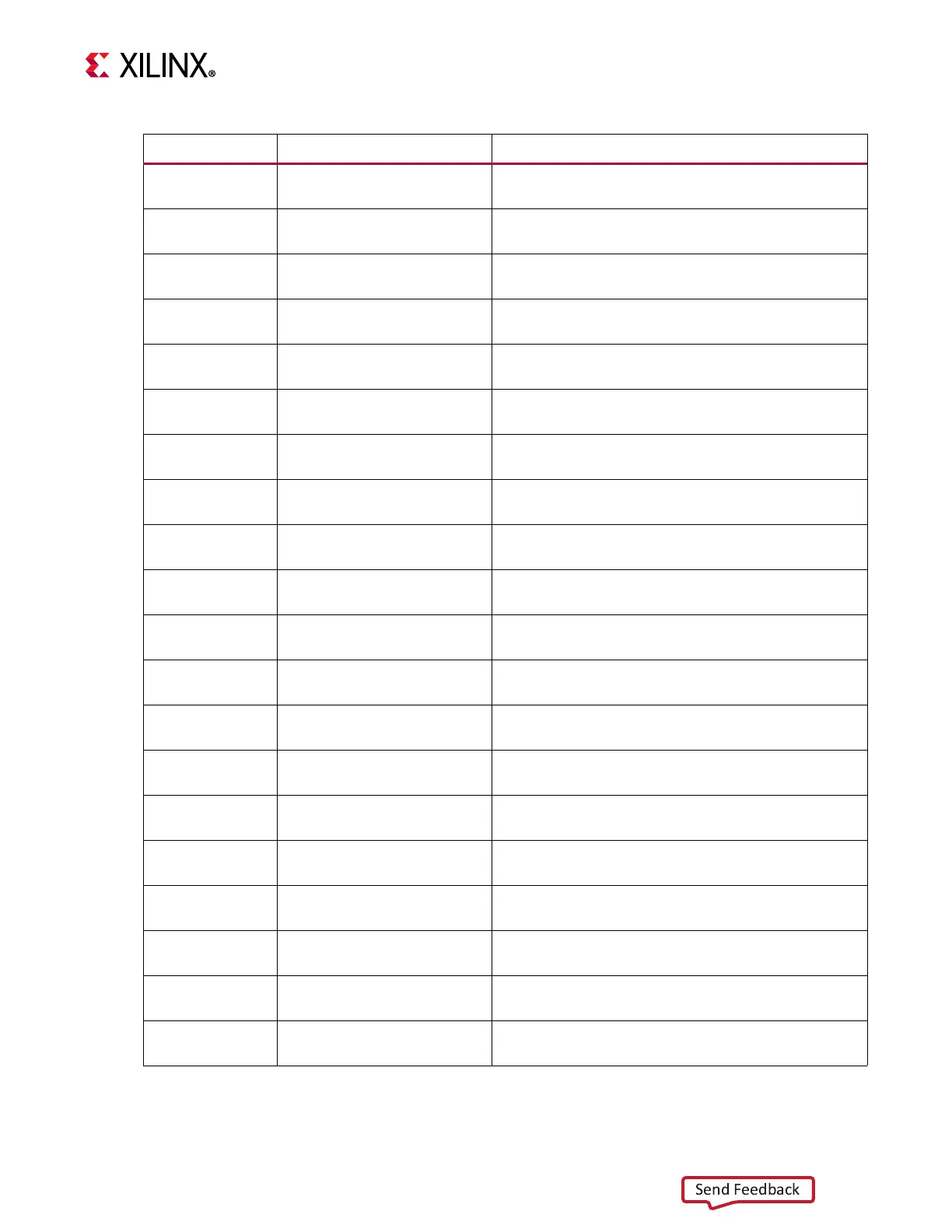

0x8C Image Information 2 for VC5

Image information 2 of the current processing packet

with VC of 5

0x90 Image Information 1 for VC6

Image information 1 of the current processing packet

with VC of 6

0x94 Image Information 2 for VC6

Image information 2 of the current processing packet

with VC of 6

0x98 Image Information 1 for VC7

Image information 1 of the current processing packet

with VC of 7

0x9C Image Information 2 for VC7

Image information 2 of the current processing packet

with VC of 7

0xA0 Image Information 1 for VC8

Image information 1 of the current processing packet

with VC of 8

0xA4 Image Information 2 for VC8

Image information 2 of the current processing packet

with VC of 8

0xA8 Image Information 1 for VC9

Image information 1 of the current processing packet

with VC of 9

0xAC Image Information 2 for VC9

Image information 2 of the current processing packet

with VC of 9

0xB0

Image Information 1 for

VC10

Image information 1 of the current processing packet

with VC of 10

0xB4

Image Information 2 for

VC10

Image information 2 of the current processing packet

with VC of 10

0xB8

Image Information 1 for

VC11

Image information 1 of the current processing packet

with VC of 11

0xBC

Image Information 2 for

VC11

Image information 2 of the current processing packet

with VC of 11

0xC0

Image Information 1 for

VC12

Image information 1 of the current processing packet

with VC of 12

0xC4

Image Information 2 for

VC12

Image information 2 of the current processing packet

with VC of 12

0xC8

Image Information 1 for

VC13

Image information 1 of the current processing packet

with VC of 13

0xCC

Image Information 2 for

VC13

Image information 2 of the current processing packet

with VC of 13

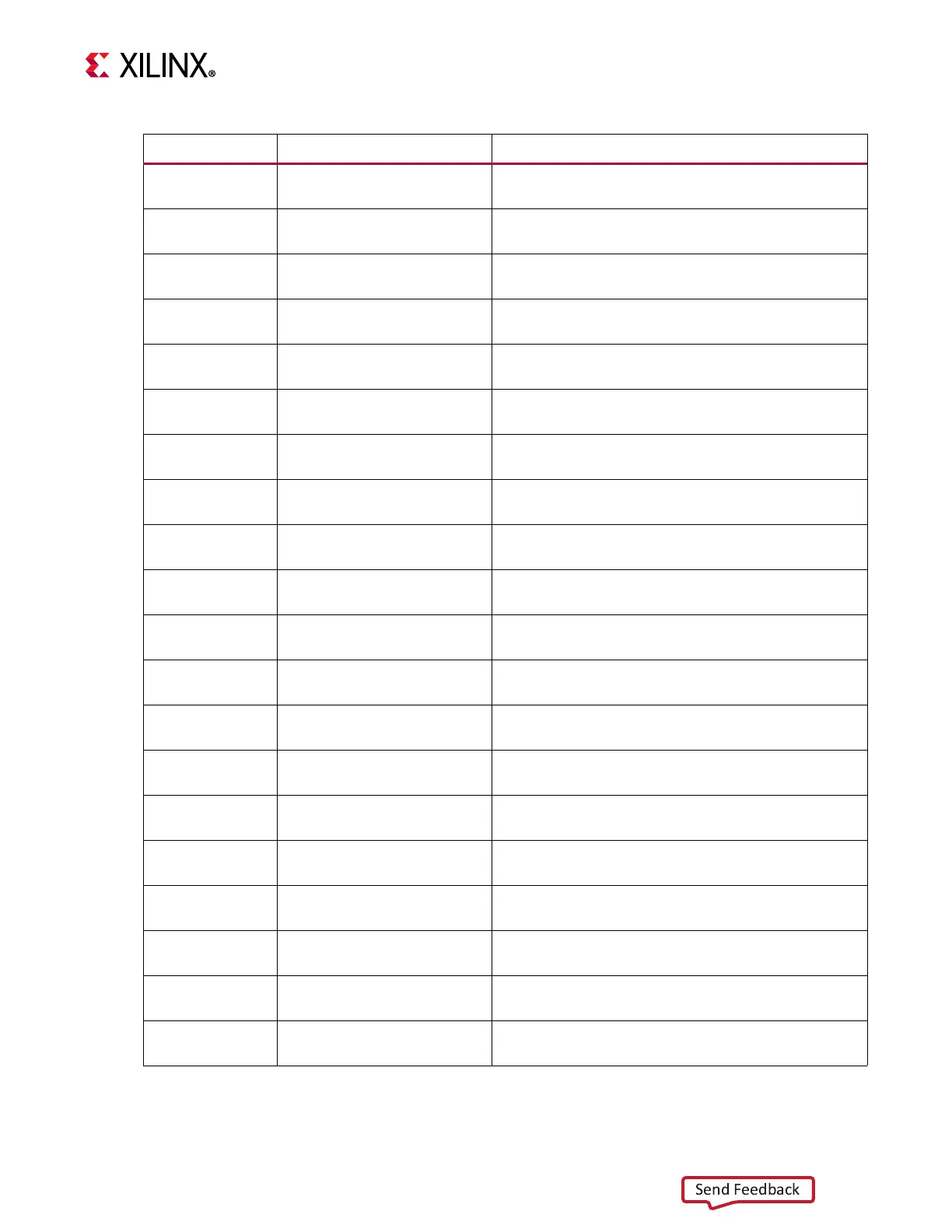

0xD0

Image Information 1 for

VC14

Image information 1 of the current processing packet

with VC of 14

0xD4

Image Information 2 for

VC14

Image information 2 of the current processing packet

with VC of 14

0xD8

Image Information 1 for

VC15

Image information 1 of the current processing packet

with VC of 15

Table 2-7: MIPI CSI-2 RX Controller Core Registers (Cont’d)

Address Offset Register Name Description

Loading...

Loading...