MIPI CSI-2 RX Subsystem v4.0 89

PG232 July 02, 2019 www.xilinx.com

Appendix C: Additional Resources and Legal Notices

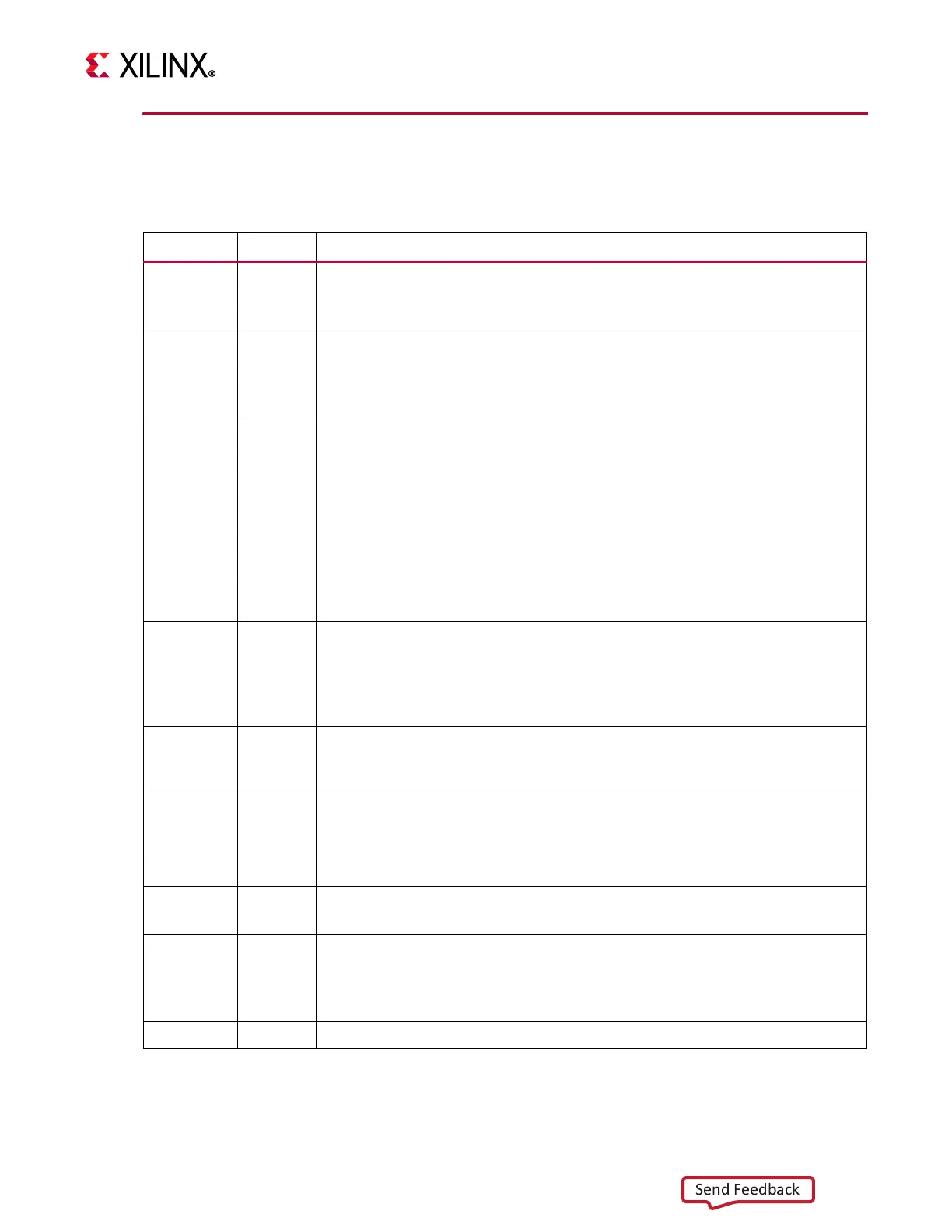

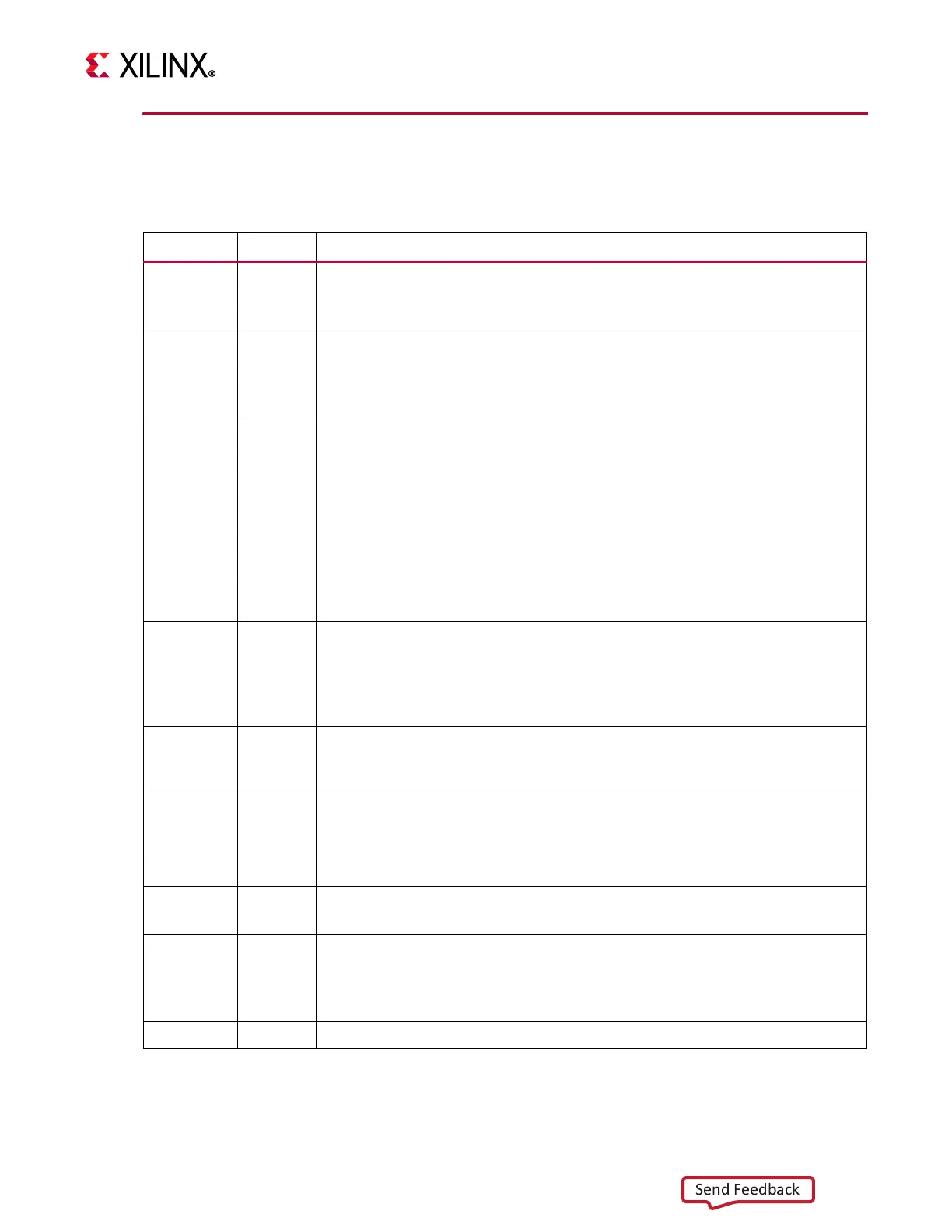

Revision History

The following table shows the revision history for this document.

Date Version Revision

07/02/2019 4.0

• Extended line rate support up to 2500 Mb/s

• Added support for Deskew sequence detection at MIPI D-PHY

• Corrected the doc version.

05/22/2019 4.1

• Updated the minimum video clock requirement in chapter 3.

• Added MIPI CSI2 RX Subsystem Latency Calculation.

• Corrected Data corruption for certain word counts during RAW20 data type

reception.

12/05/2018 4.0

• Updated video_out_tdest and emb_nonimg_tdest port size.

• Updated Table 2-5 to include VCX Frame Error register, Image Information 1,

and Image Information 2 Registers for VC4 to VC15.

• Updated Table 1-1 to include RAW16, RAW20, and YUV 422 10 bit data types.

• Updated Table 4-1 User Parameters.

• Included new GUI options for MIPI CSI-2 Standard v2.0 compatibility in the

Configuration Tab.

• Updated examples in the Pixel Packing for Multiple Data Types section to

match the alignment described in AXI4-Stream Video IP and System Design

Guide (UG934).

04/04/2018 3.0

• ECC and CRC of long packets are made available on TUSER ports of output

stream interfaces.

• Added support for additional 7 series devices.

• Added dynamic configuration capability for IDELAY Tap values in fixed

calibration mode of 7 series.

10/04/2017 3.0

• Added Application Example Design to demonstrate a full end-to-end system

from capture to display on ZCU102

• Added Board automation support for LI-IMX274MIPI-FMC V1.0 FMC model

04/05/2017 2.2

• Word Count (WC) corruption limited to current packet. Additional bit in ISR

added to report this conditions

• MIPI DPHY v3.1 changes integrated

11/30/2016 2.1

• Added calibration mode parameters for FIXED and AUTO modes

10/05/2016 2.1

• MIPI D-PHY 3.0 changes integrated

• Added 7 Series support

04/06/2016 2.0

• MIPI D-PHY 2.0 changes integrated

• Shared logic support

• Video Format Bridge core changes to support RAW8 and User Defined

Byte-based Data at all times along with the Vivado IDE selected data type.

11/18/2015 1.0

Initial Xilinx release.

Loading...

Loading...