MIPI CSI-2 RX Subsystem v4.0 15

PG232 July 02, 2019 www.xilinx.com

Chapter 2: Product Specification

D-PHY latency:

The MIPI D-PHY RX core latency is the time from the start-of-transmission (SoT) pattern on

the serial lines to the activehs signal assertion on the PPI .The HS_SETTLE period contributes

significantly in the D-PHY latency calculation.

Tab l e 2 - 1 provides the latency numbers for various core configurations.

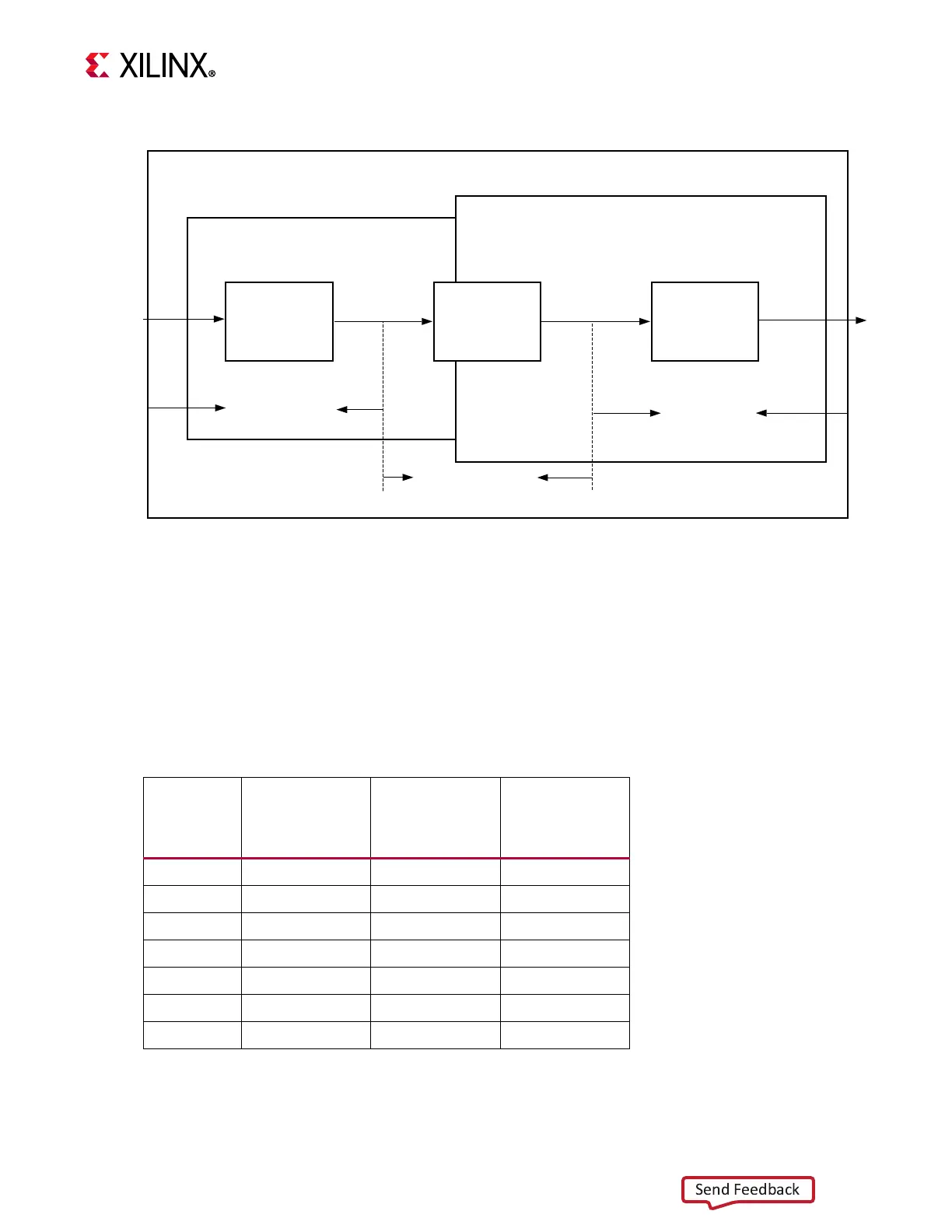

X-Ref Target - Figure 2-1

Figure 2-1: MIPI CSI2 RX Subsystem Latency Calculation

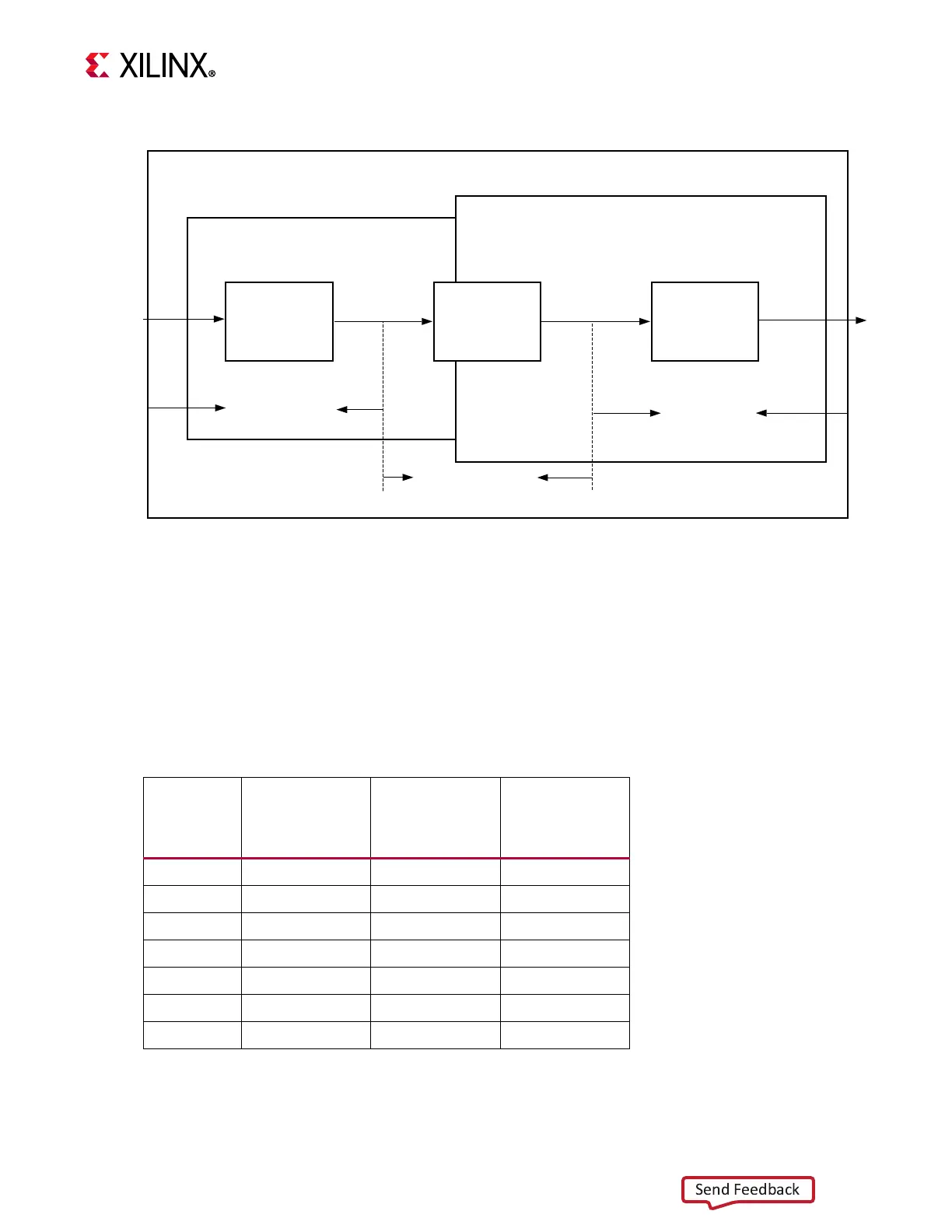

Table 2-1: D-PHY Latency

Data Type Pixel Mode Line Rate

Latency in

rxbyteclk

(HS_SETTLE +

internal latency)

RAW20 Single

1000 26(23+3)

RAW8 Single

1000 26(23+3)

RAW8 Dual

1000 26(23+3)

RAW8 Quad

1000 26(23+3)

RAW10 Single

1000 26(23+3)

RAW10 Dual

1200 30(26+4)

RAW10 Quad

800 22(20+2)

Notes: All the calculations are made for a single lane design with a fixed

video clock of 148 MHz.

1-4-'76<79&7=78)1

(4,= :*&

V\F]XIGPO(SQEMR

:MHIS'PSGO(SQEMR

7IVMEP0MRIW

(4,=0EXIRG]

'SRXVSPPIV0EXIRG]

:*&0EXIRG]

44-

7XVIEQMRK-*

7XVIEQMRK-*

1-4-'7-6<

'SRXVSPPIV

<

Loading...

Loading...