MIPI CSI-2 RX Subsystem v4.0 47

PG232 July 02, 2019 www.xilinx.com

Chapter 3: Designing with the Subsystem

• For a MIPI interface with 1000 Mb/s per lane, 1 lane, quad pixel mode design

processing RAW10 data, the minimum required video clock is (1000 * 1) / 4 / 10 or

higher. Where 10 represents the number of bits in one RAW10 pixel.

• Below is the equation used to calculate the minimum required video clock

video_aclk1(MHz) = Line Rate(Mb/s) * Data Lanes / 8 / 4

video_aclk2(MHz) = (Line Rate(Mb/s) * Data Lanes) / Pixel Mode /

Number of Bits Per Pixel

The effective minimun required video clock is:

video_aclk(MHz) = Max { video_aclk1 , video_aclk2}

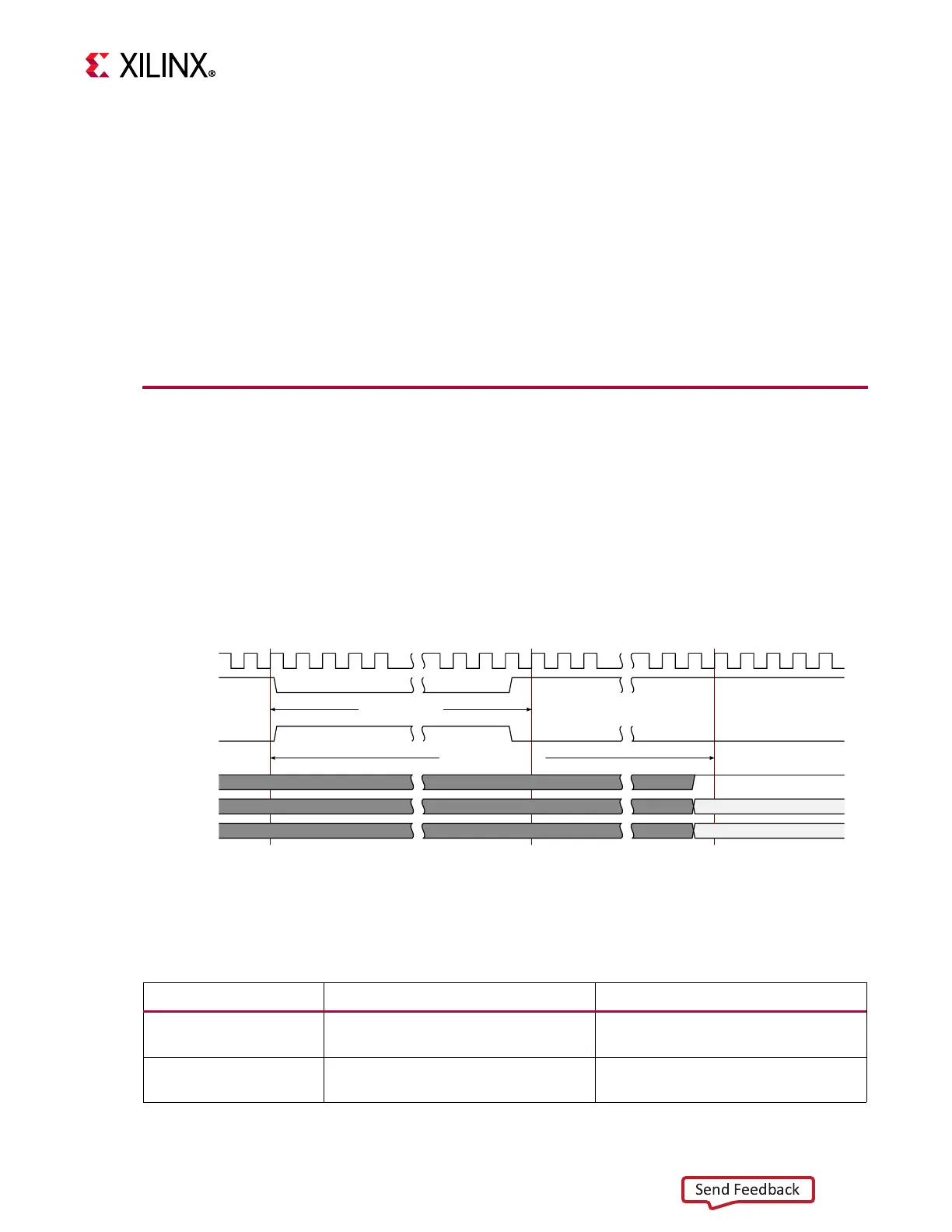

Resets

The subsystem has two reset ports:

• lite_aresetn: Active-Low reset for the AXI4-Lite register interface.

• video_aresetn: Active-Low reset for the subsystem blocks.

The duration of video_aresetn should be a minimum of 40 dphy_clk_200M cycles to

propagate the reset throughout the system. See Figure 3-8.

Tab l e 3 - 3 summarizes all resets available to the MIPI CSI-2 RX Subsystem and the

components affected by them.

X-Ref Target - Figure 3-8

Figure 3-8: MIPI CSI-2 RX Reset

Table 3-3: Resets

Sub-core Lite_aresetn Video_aresetn

MIPI CSI-2 RX Controller

Connected to s_axi_aresetn core

port

Connected to

m_axis_aresetn

core

port

MIPI D-PHY

Connected to s_axi_aresetn core

port

Inverted signal connected to core_rst

core port

video_aclk

video_aresetn

core_rst(DPHY)

stopstate

cp/cn

dp/dn

LP-11

LP-11

dphy_clk_200M of 40 cycles

Power on reset sequence for DPHY

Loading...

Loading...