MIPI CSI-2 RX Subsystem v4.0 4

PG232 July 02, 2019 www.xilinx.com Product Specification

Introduction

The Mobile Industry Processor Interface (MIPI)

Camera Serial Interface (CSI-2) RX subsystem

implements a CSI-2 receive interface according

to the MIPI CSI-2 standard v2.0 [Ref 1] with

underlying MIPI D-PHY standard v1.2. The

subsystem captures images from MIPI CSI-2

camera sensors and outputs AXI4-Stream video

data ready for image processing. The

subsystem allows fast selection of the top level

parameters and automates most of the lower

level parameterization. The AXI4-Stream video

interface allows a seamless interface to other

AXI4-Stream-based subsystems.

Features

• Support for 1 to 4 D-PHY lanes

• Line rates ranging from 80 to 2500Mb/s

• Multiple Data Type support (RAW, RGB, YUV)

• AXI IIC support for Camera Control

Interface (CCI)

• Filtering based on Virtual Channel Identifier

• Support for 1, 2, or 4 pixels per sample at

the output as defined in the Xilinx

AXI4-Stream Video IP and System Design

Guide (UG934) [Ref 2] format

• AXI4-Lite interface for register access to

configure different subsystem options

• Dynamic selection of active lanes within the

configured lanes during subsystem

generation.

• Interrupt generation to indicate subsystem

status information

• Internal D-PHY allows direct connection to

image sources

• Support for MIPI CSI-2 standard v2.0

features such as VCX, RAW16, and RAW20

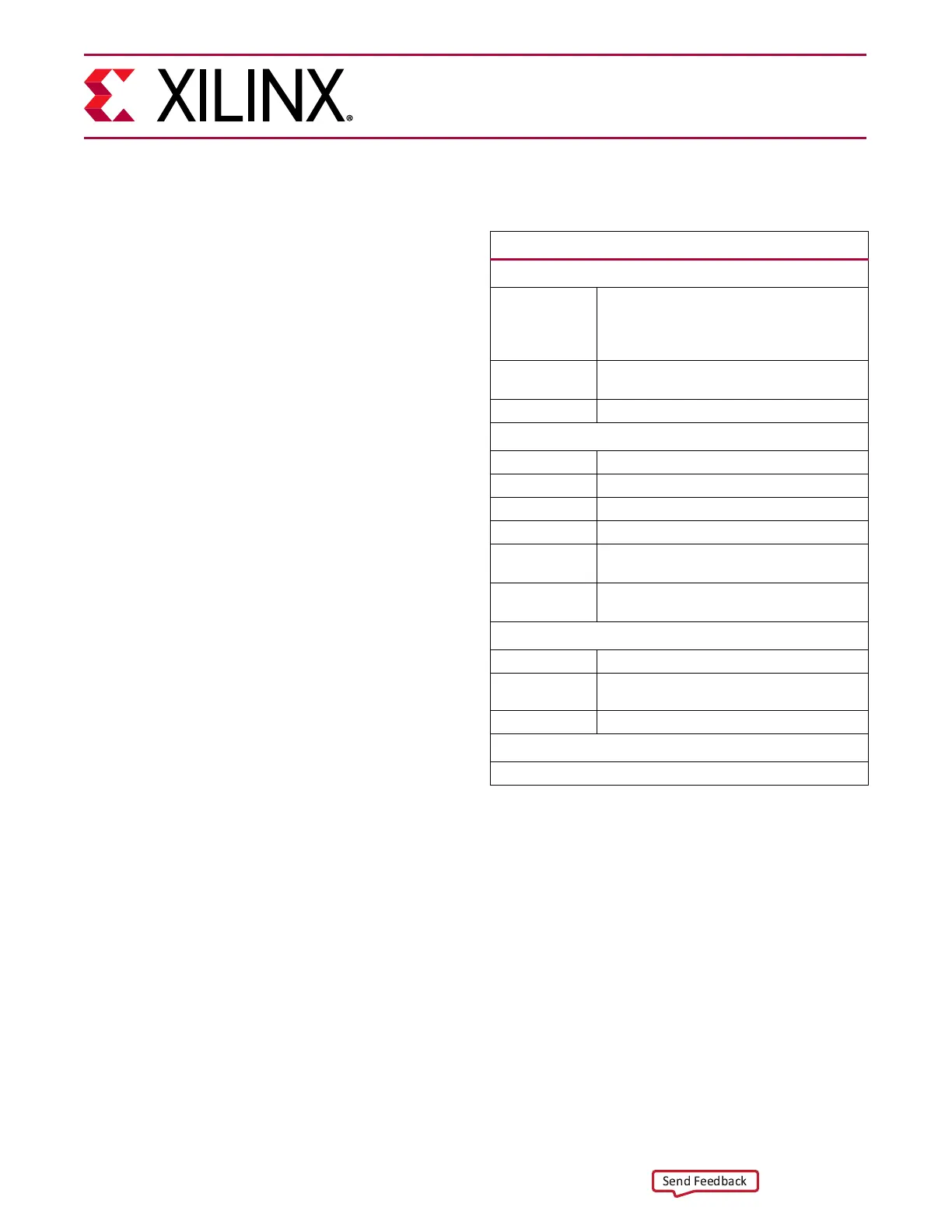

IP Facts

IP Facts Table

Subsystem Specifics

Supported

Device Family

(1)

UltraScale+™,

Zynq® UltraScale+ MPSoC,

Zynq®-7000 SoC,

7 Series FPGAs

Supported User

Interfaces

AXI4-Lite, AXI4-Stream

Resources Performance and Resource Utilization web page

Provided with Subsystem

Design Files Encrypted RTL

Example Design Vivado IP Integrator

Test Bench Not Provided

Constraints File XDC

Simulation

Model

Not Provided

Supported

S/W Driver

(2)

Standalone and Linux

Tested Design Flows

(3)

Design Entry Vivado® Design Suite

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete list of supported devices, see the Vivado IP

catalog.

2. Standalone driver details can be found in the SDK directory

(<install_directory>/SDK/<release>/data/embeddedsw/doc/

xilinx_drivers.htm). Linux OS and driver support information

is available from the

Xilinx Wiki page.

3. For the supported versions of the tools, see the

Xilinx Design Tools: Release Notes Guide.

Loading...

Loading...