MIPI CSI-2 RX Subsystem v4.0 10

PG232 July 02, 2019 www.xilinx.com

Chapter 1: Overview

Example 2: RAW7 and Four Pixels per Clock Selected in the Vivado IDE

• Single pixel width of RAW7 = 7

• Single pixel width of RAW8 = 8

With four pixels per clock selected, the effective pixels widths are 28 and 32 for RAW7 and

RAW8 respectively. The video_out port width is configured as the maximum of the

individual pixel widths, and rounded to nearest byte boundary. This results in a video_out

port width of 32.

Pixel Packing for Multiple Data Types

When multiple pixels are transferred with different pixel width, the pixels with lower width

are justified to most significant bits.

Example 1

When RAW12 and RAW8 are transferred with two pixels per clock, the data port width of the

video_out interface is 24-bits. Within the 24-bits the RAW8 pixels are aligned to the most

significant bits as shown in the following table:

IMPORTANT: In a multi pixel scenario pixel width varies, pixels with lower width are justified to the

most significant bit.

Example 2

When the core is configured with RAW6 and two pixels per clock, the video_out port

width is set to 16-bits. Within the 16-bits the RAW6 and RAW8 pixels are aligned to the

most significant bits as shown in the following table:

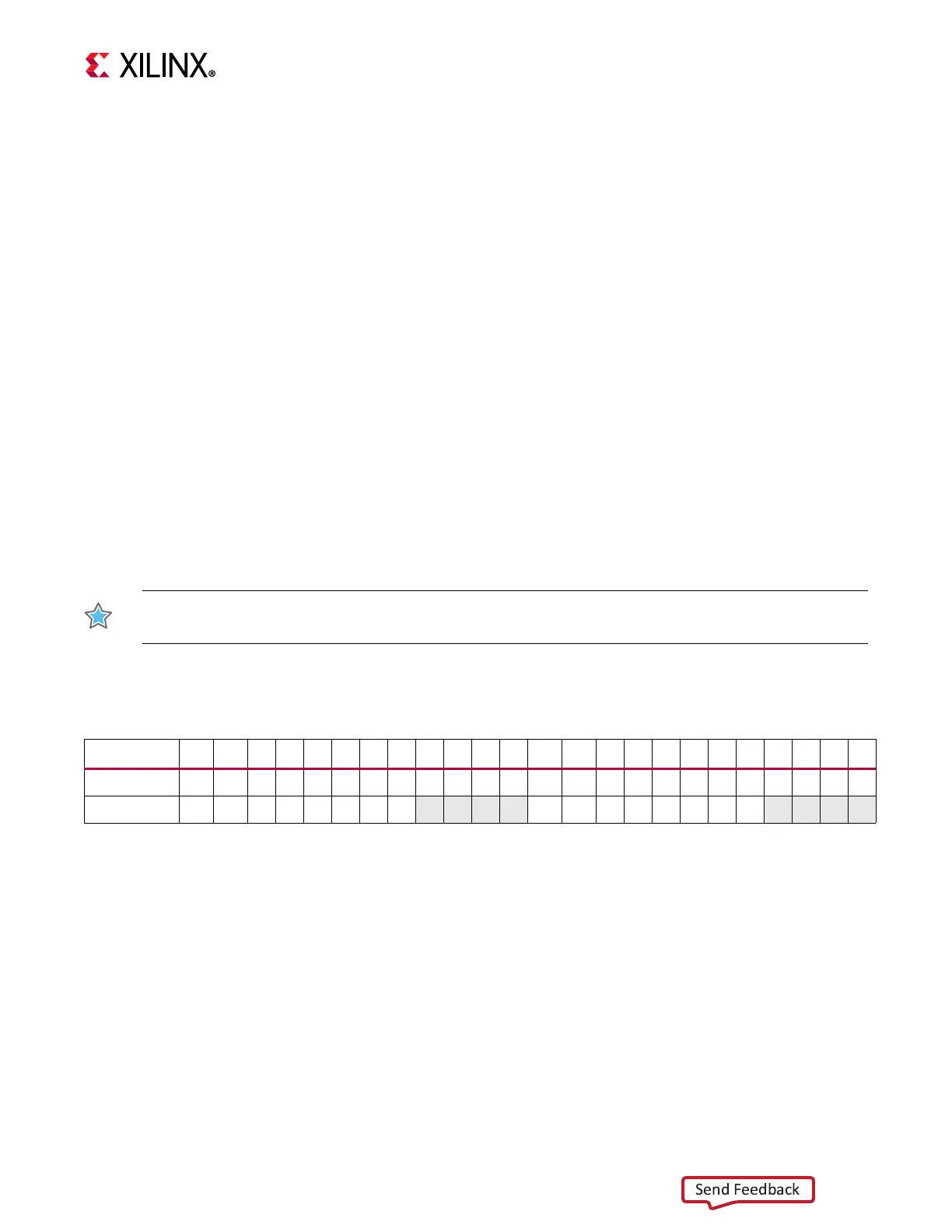

Table 1-2: Pixel Packing for RAW12 and RAW8 Data Types

Bit Positions23222120191817161514131211109876543210

RAW12

q11 q10 q9 q8 q7 q6 q5 q4 q3 q2 q1 q0 p11 p10 p9 p8 p7 p6 p5 p4 p3 p2 p1 p0

RAW8

q7 q6 q5 q4 q3 q2 q1 q0 p7 p6 p5 p4 p3 p2 p1 p0

Notes:

1. p0 to p11 is the 1st pixel bits of RAW12; q0 to q11 is the 2nd pixel bits of RAW12.

2. p0 to p7 is the 1st pixel bits of RAW8; q0 to q7 is the 2nd pixel bits of RAW8.

Loading...

Loading...