MIPI CSI-2 RX Subsystem v4.0 20

PG232 July 02, 2019 www.xilinx.com

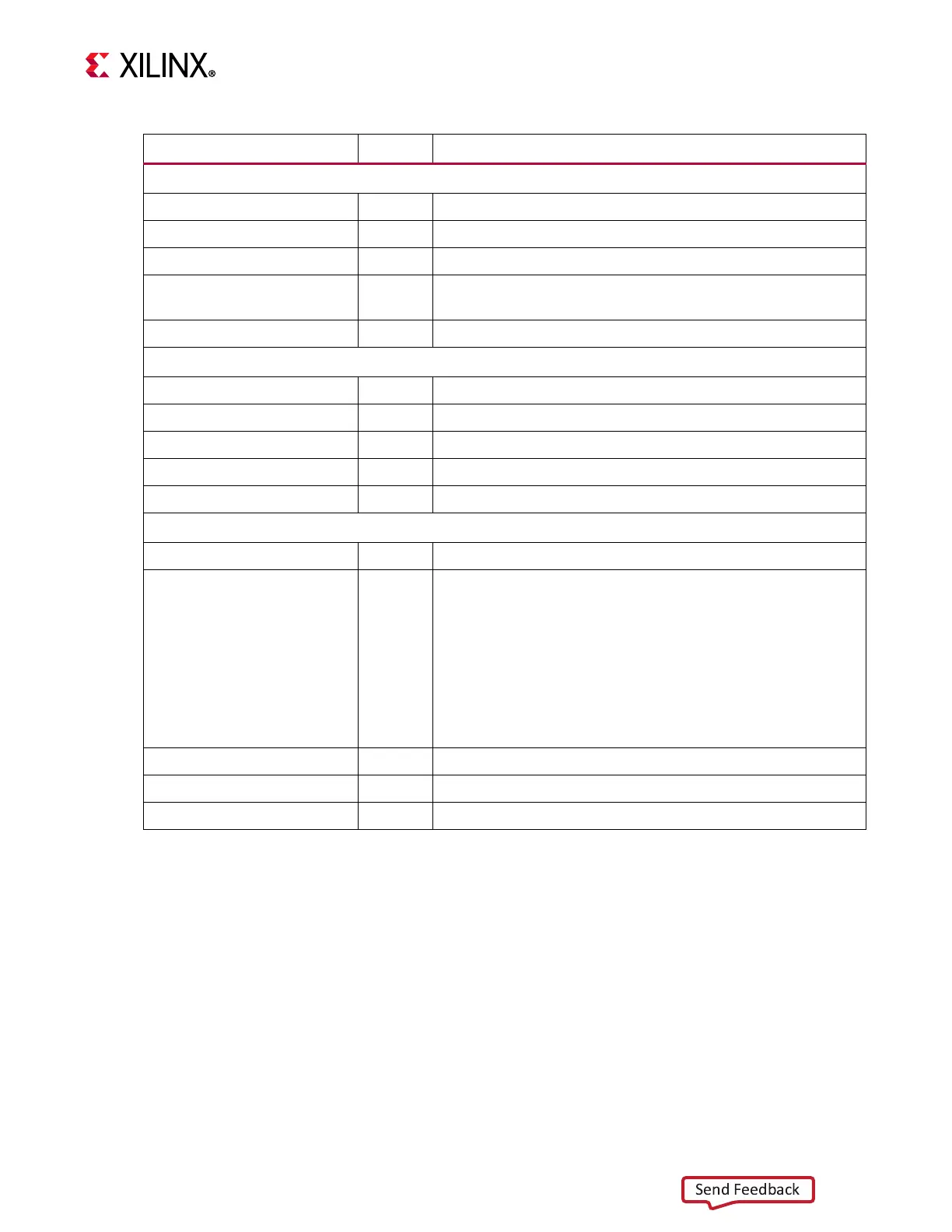

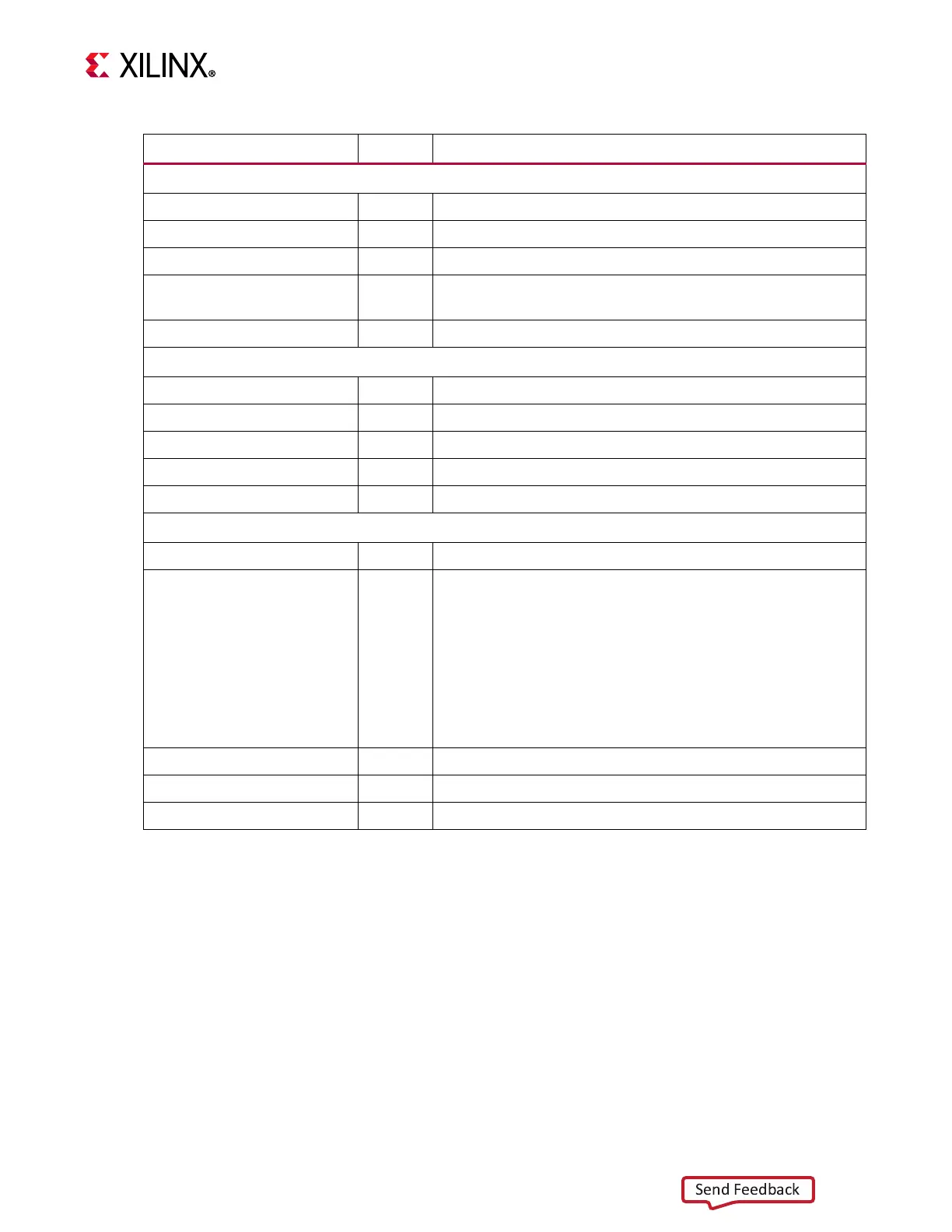

Chapter 2: Product Specification

Xilinx 7 series FPGA

mipi_dphy_if Output DPHY interface

rxbyteclkhs Output PPI high-speed receive byte clock

system_rst_out Output Reset indication due to PLL reset (active-High)

dlyctrl_rdy_out Output

Ready signal output from IDEALYCTRL, stating delay values

are adjusted as per vtc changes

clk_300m Input 300 MHz clock for IDELAYCTRL

UltraScale+ Shared Logic outside Subsystem

mipi_phy_if Output DPHY interface

rxbyteclkhs Output PPI high-speed receive byte clock

clkoutphy_out Output PHY serial clock

system_rst_out Output Reset indication due to PLL reset (active-High)

pll_lock_out Output PLL lock indication (active-High)

UltraScale+ Shared logic in the Subsystem

mipi_phy_if Output DPHY interface

bg<x>_pin<y>_nc Input

Inferred bitslice ports. The core infers bitslice0 of a nibble for

strobe propagation within the byte group; <x> indicates byte

group (0,1,2,3); <y> indicates bitslice0 position (0 for the

lower nibble, 6 for the upper nibble)

• RTL Design: There is no need to drive any data on these

ports.

• IP Integrator: These ports must be brought to the top level

of the design to properly apply the constraints.

Note:

Pins are available only for UltraScale+ families.

clkoutphy_in Input PHY serial clock

pll_lock_in Input PLL Lock indication

rxbyteclkhs Output PPI high-speed receive byte clock

Notes:

1. The active-High reset for the MIPI D-PHY core is generated internally by setting the external

active-Low reset (video_aresetn) to 0.

2. Each frame start packet with Virtual Channel (VC) identifier will be mapped to the first image packet and the first

embedded non-image with the corresponding VC.

3. As CRC appears at the end of the MIPI packet, ECC and CRC are reported ONLY during the last beat of the stream

transfer when TLAST and TVALID are asserted. You need to ignore ECC/CRC reported during other beats of the

transfer. See Interface Debug for more details.

Table 2-5: Port Descriptions (Cont’d)

Signal Name Direction Description

Loading...

Loading...