MIPI CSI-2 RX Subsystem v4.0 7

PG232 July 02, 2019 www.xilinx.com

Chapter 1: Overview

Features of this core include:

• 1–4 lane support, with register support to select active lanes (the actual number of

available lanes to be used)

• Short and long packets with all word count values supported

• Primary and many secondary video formats supported

• Data Type (DT) interleaving

• Virtual Channel Identifier (VC) interleaving

• Combination of Data Type and VC interleaving

• Multi-lane interoperability

• Error Correction Code (ECC) for 1-bit error correction and 2-bit error detection in

packet header

• CRC check for payload data

• Long packet ECC/CRC forwarding capability for downstream IPs

• Maximum data rate of 2.5 Gb/s

• Pixel byte packing based on data format

• AXI4-Lite interface to access core registers

• Low power state detection

• Error detection (D-PHY Level Errors, Packet Level Errors, Protocol Decoding Level Errors)

• AXI4-Stream interface with 32/64-bit TDATA width support to offload pixel information

externally

• Interrupt support for indicating internal status/error information

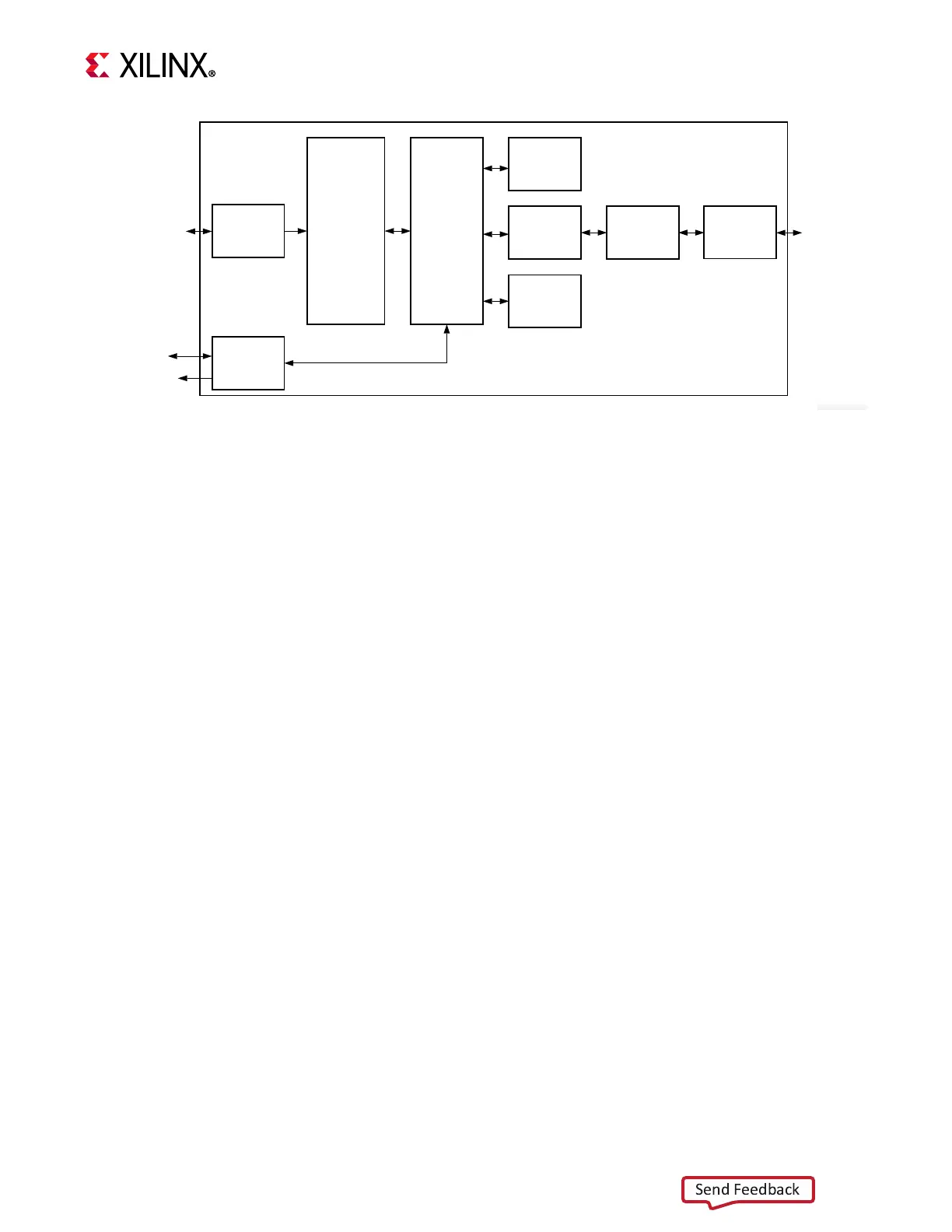

X-Ref Target - Figure 1-2

Figure 1-2: MIPI CSI-2 RX Controller Core

PHY Protocol

Interface

(PPI)

Lane

Management

Control

FSM

PHECC

Processing

Data

Processing

CRC

Checker

Buffer

AXI4-

Stream

Register

Interface

AXI4-Stream

PPI

AXI4-Lite

Interrupt

X16317-031116

Loading...

Loading...