MIPI CSI-2 RX Subsystem v4.0 27

PG232 July 02, 2019 www.xilinx.com

Chapter 2: Product Specification

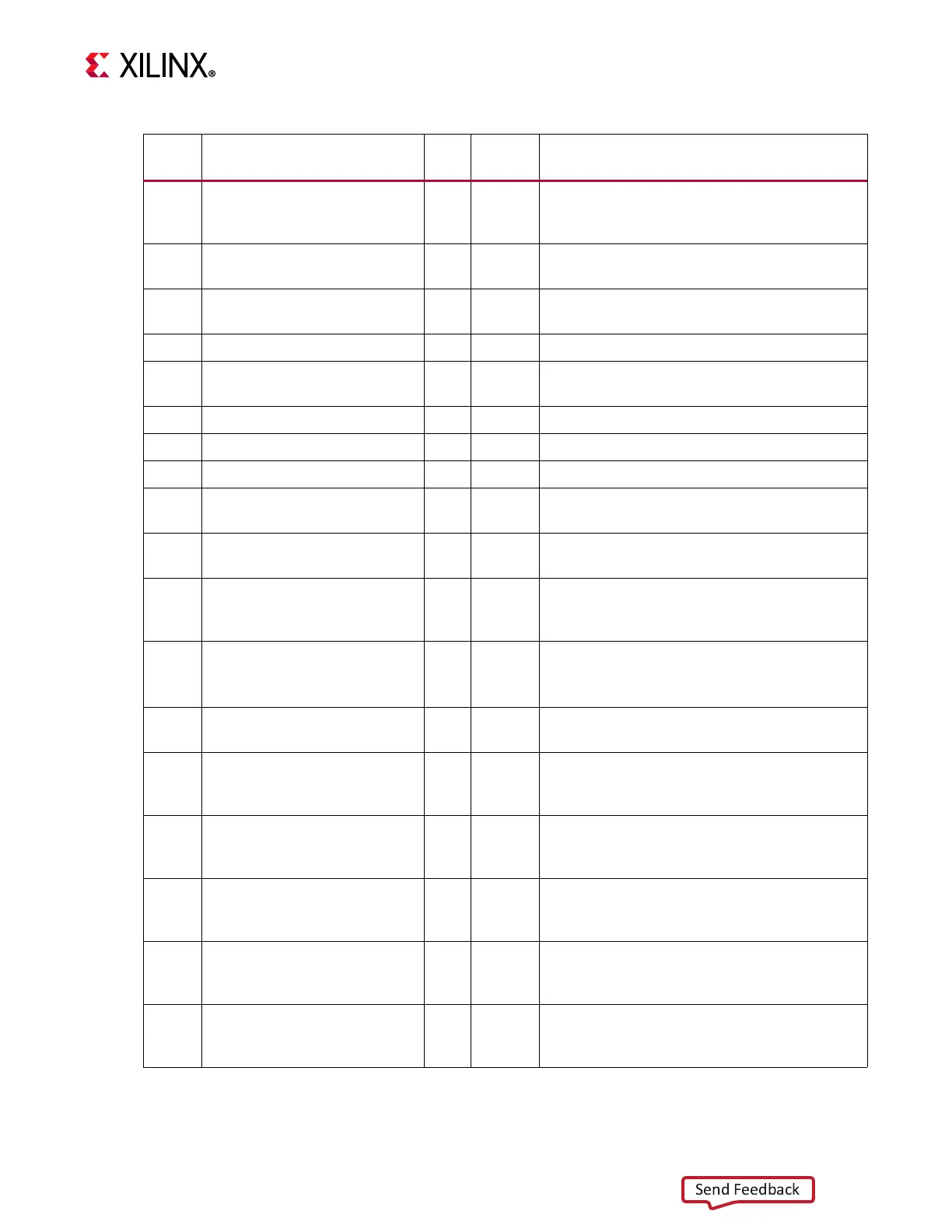

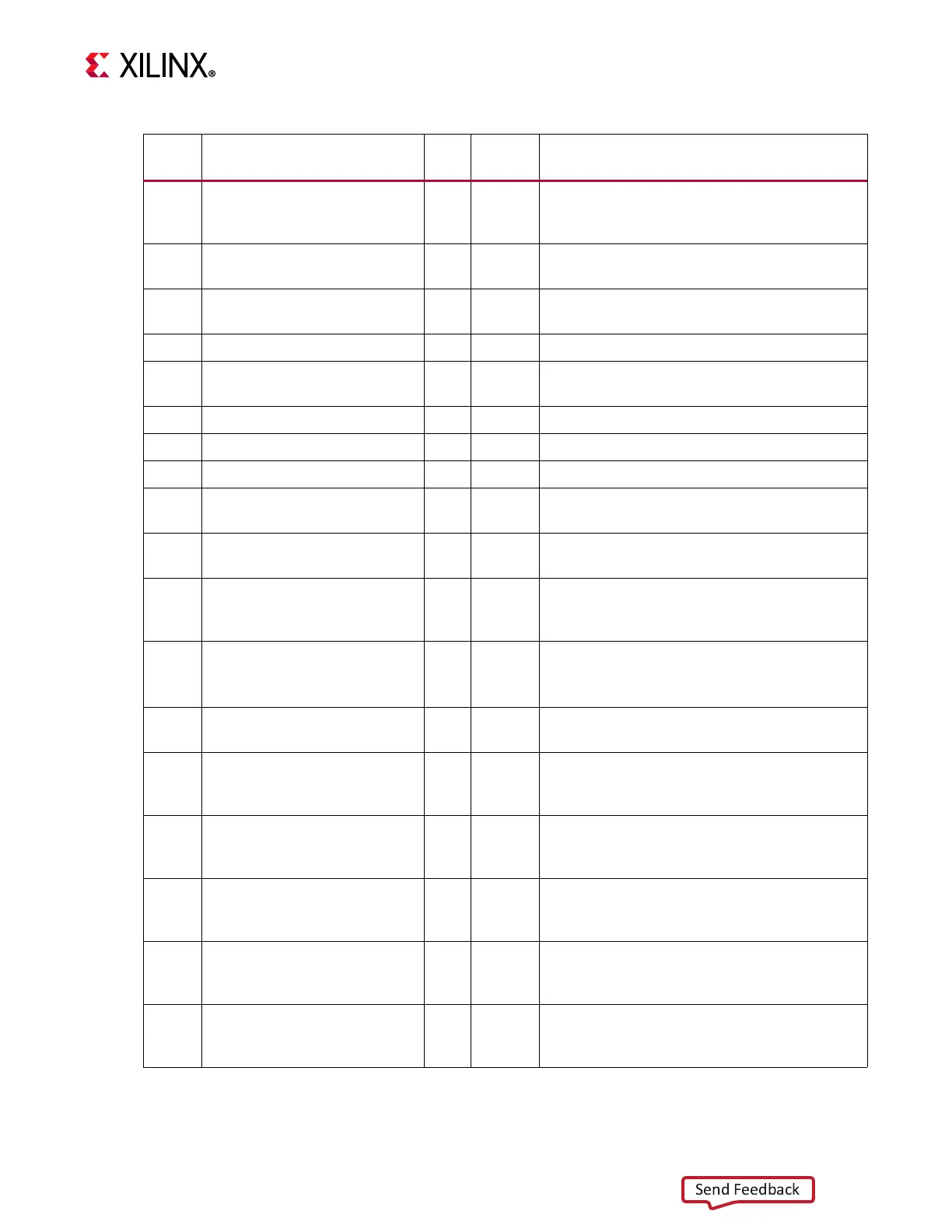

21 Incorrect lane configuration 0x0 R/W1C

Asserted when Active lanes is greater than

Maximum lanes in the protocol configuration

register

20 Short packet FIFO full 0x0 R/W1C

Active-High signal asserted when the short

packet FIFO full condition detected

19 Short packet FIFO not empty 0x0 R/W1C

Active-High signal asserted when short

packet FIFO not empty condition detected

18 Stream line buffer full 0x0 R/W1C Asserts when the line buffer is full

(2)

17 Stop state 0x0 R/W1C

Active-High signal indicates that the lane

module is currently in Stop state

(3)

16 Reserved N/A N/A N/A

15 Reserved N/A N/A N/A

14 Reserved N/A N/A N/A

13

SoT error

(ErrSoTHS)

0x0 R/W1C

Indicates Start-of-Transmission (SoT) error

detected

(3)

12

SoT sync error

(ErrSotSyncHS)

0x0 R/W1C

Indicates SoT synchronization completely

failed

(3)

11

ECC 2-bit error

(ErrEccDouble)

0x0 R/W1C

Asserted when an ECC syndrome is computed

and two bit errors detected in the received

packet header

10

ECC 1-bit error

(Detected and Corrected)

(ErrEccCorrected)

0x0 R/W1C

Asserted when an ECC syndrome was

computed and a single bit error in the packet

header was detected and corrected

9

CRC error

(ErrCrc)

0x0 R/W1C

Asserted when the computed CRC code is

different from the received CRC code

8

Unsupported Data Type

(ErrID)

0x0 R/W1C

Asserted when a packet header is decoded

with an unrecognized or not implemented

data ID

7

Frame synchronization

error for VC3

(ErrFrameSync)

0x0 R/W1C

Asserted when an FE is not paired with a

Frame Start (FS) on the same virtual channel

(4)

6

Frame level error for VC3

(ErrFrameData)

0x0 R/W1C

Asserted after an FE when the data payload

received between FS and FE contains errors.

The data payload errors are CRC errors.

5

Frame synchronization

error for VC2

(ErrFrameSync)

0x0 R/W1C

Asserted when an FE is not paired with a FS on

the same virtual channel

(4)

4

Frame level error for VC2

(ErrFrameData)

0x0 R/W1C

Asserted after an FE when the data payload

received between FS and FE contains errors.

The data payload errors are CRC errors.

Table 2-12: Interrupt Status Register (0x24) (Cont’d)

Bits Name

Reset

Value

Access

(1)

Description

Loading...

Loading...