Zynq-7000 PCB Design Guide www.xilinx.com 33

UG933 (v1.8) November 7, 2014

Chapter 3: Power Distribution System

• Place the oscilloscope in infinite persistence mode to acquire all noise over a long time

period (many seconds or minutes). If the design operates in many different modes,

using different resources in different amounts, these various conditions and modes

should be in operation while the oscilloscope is acquiring the noise measurement.

• Place the oscilloscope in averaging mode and trigger on a known aggressor event. This

can show the amount of noise correlated with the aggressor event (any events

asynchronous to the aggressor are removed through averaging).

Power system noise measurements should be made at a few different AP SoC locations to

ensure that any local noise phenomena are captured.

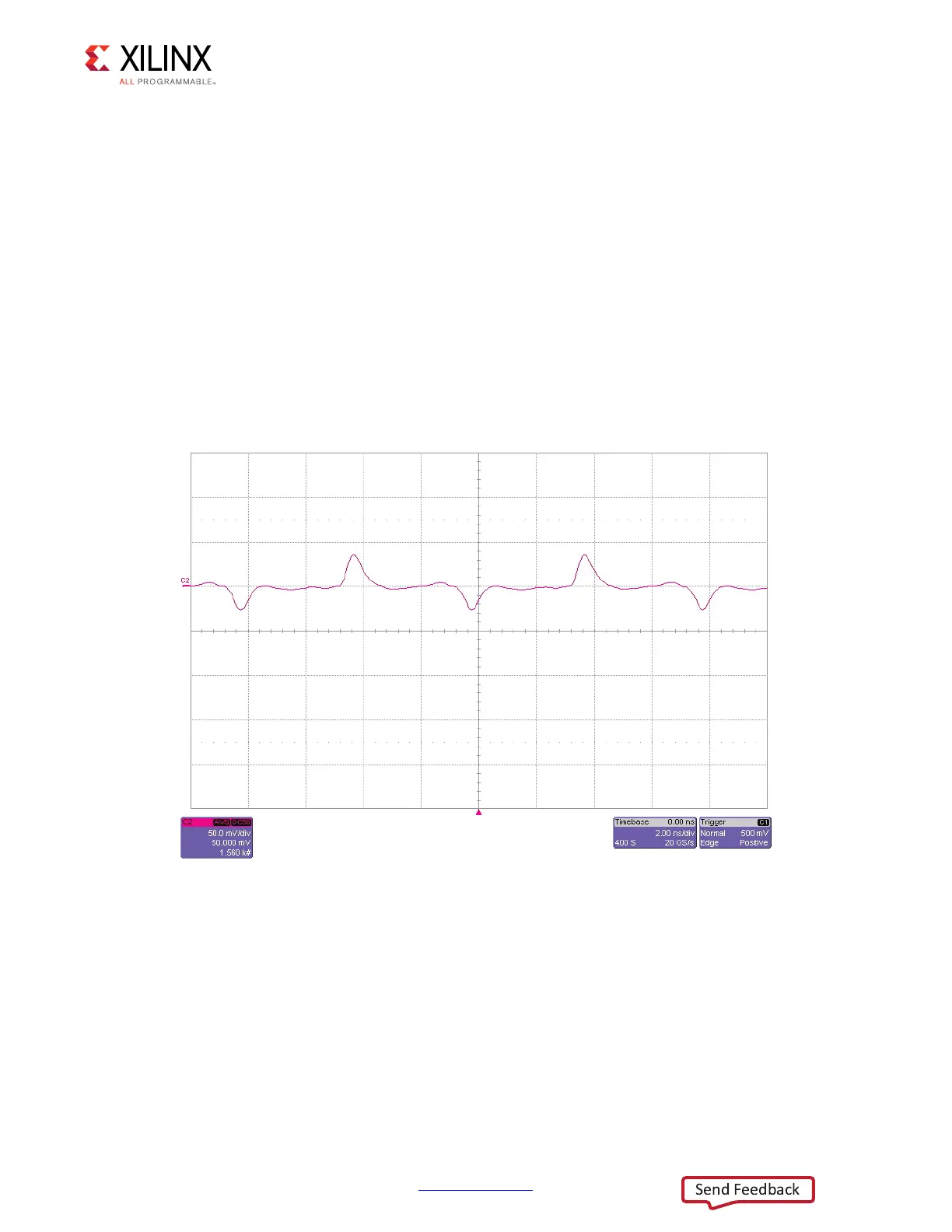

Figure 3-8 shows an averaged noise measurement taken at the V

CCO

pins of a sample

design. In this case, the trigger was the clock for an I/O bus interface sending a 1-0-1-0

pattern at 250 Mb/s.

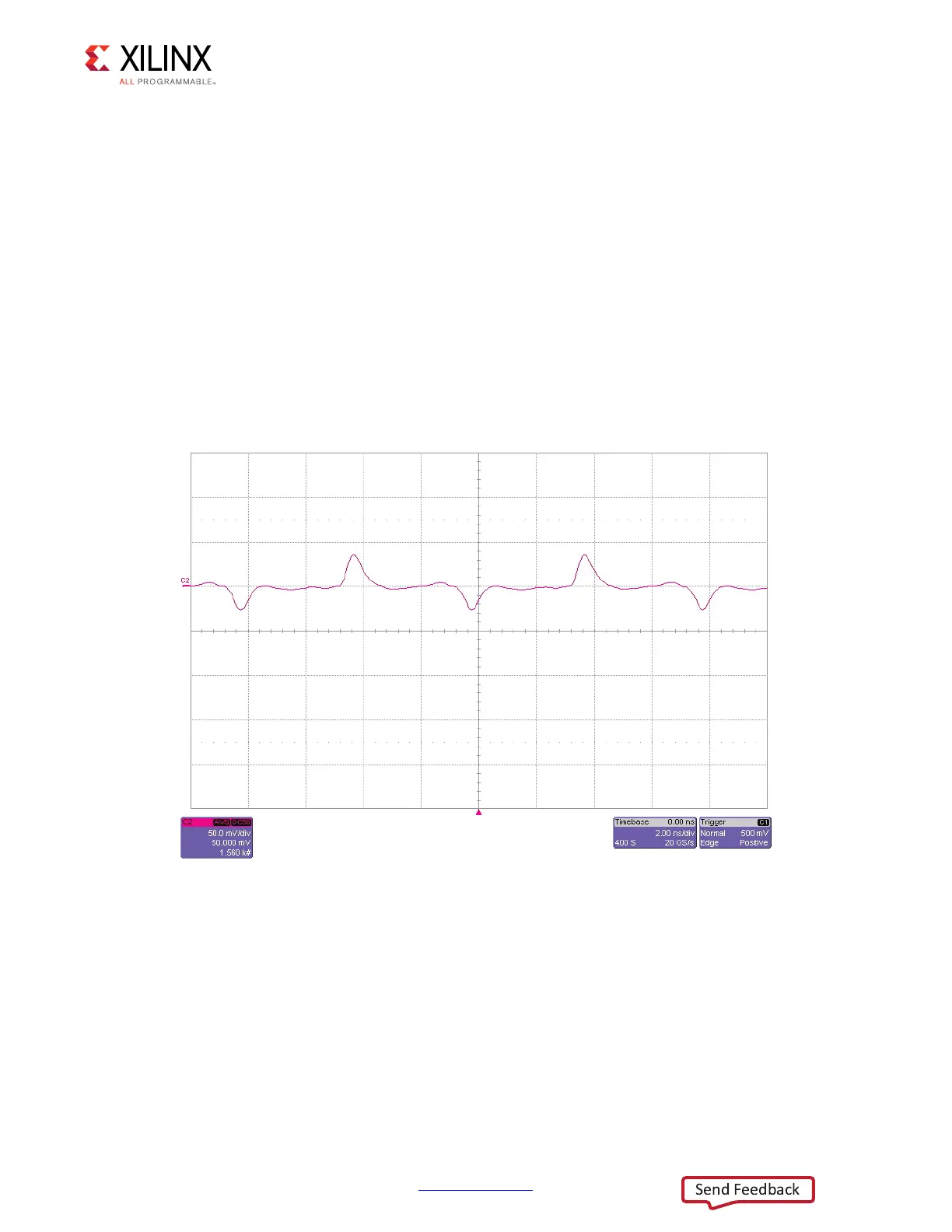

Figure 3-9 shows an infinite persistence noise measurement of the same design with a

wider variety of I/O activity. Because the infinite persistence measurement catches all noise

events over a long period, both correlated and non-correlated with the primary aggressor,

all power system excursions are shown.

X-Ref Target - Figure 3-8

Figure 3-8: Averaged Measurement of V

CCO

Supply with Multiple I/O Sending Patterns at 250 Mb/s

UG933_c3_08_032811

Loading...

Loading...