Configuration Function Pin Type Direction Powered by

TDO

(8)

Fixed Output V

CCIO_SDM

nSTATUS

SDM I/O Output V

CCIO_SDM

nCONFIG

SDM I/O Input V

CCIO_SDM

MSEL[2:0]

SDM I/O, Dual-Purpose Input V

CCIO_SDM

Note:

Although the CONF_DONE and INIT_DONE configuration signals are not required, Intel recommends that you use these

signals. The SDM drives the CONF_DONE signal high after successfully receiving full bitstream. The SDM drives the

INIT_DONE signal high to indicate the device is fully in user mode.

Note: Pin-Out files are not yet available for Intel Agilex devices.Intel Agilex

Related Information

Programming Support for Jam STAPL Language

3.4.1. JTAG Configuration Scheme Hardware Components and File Types

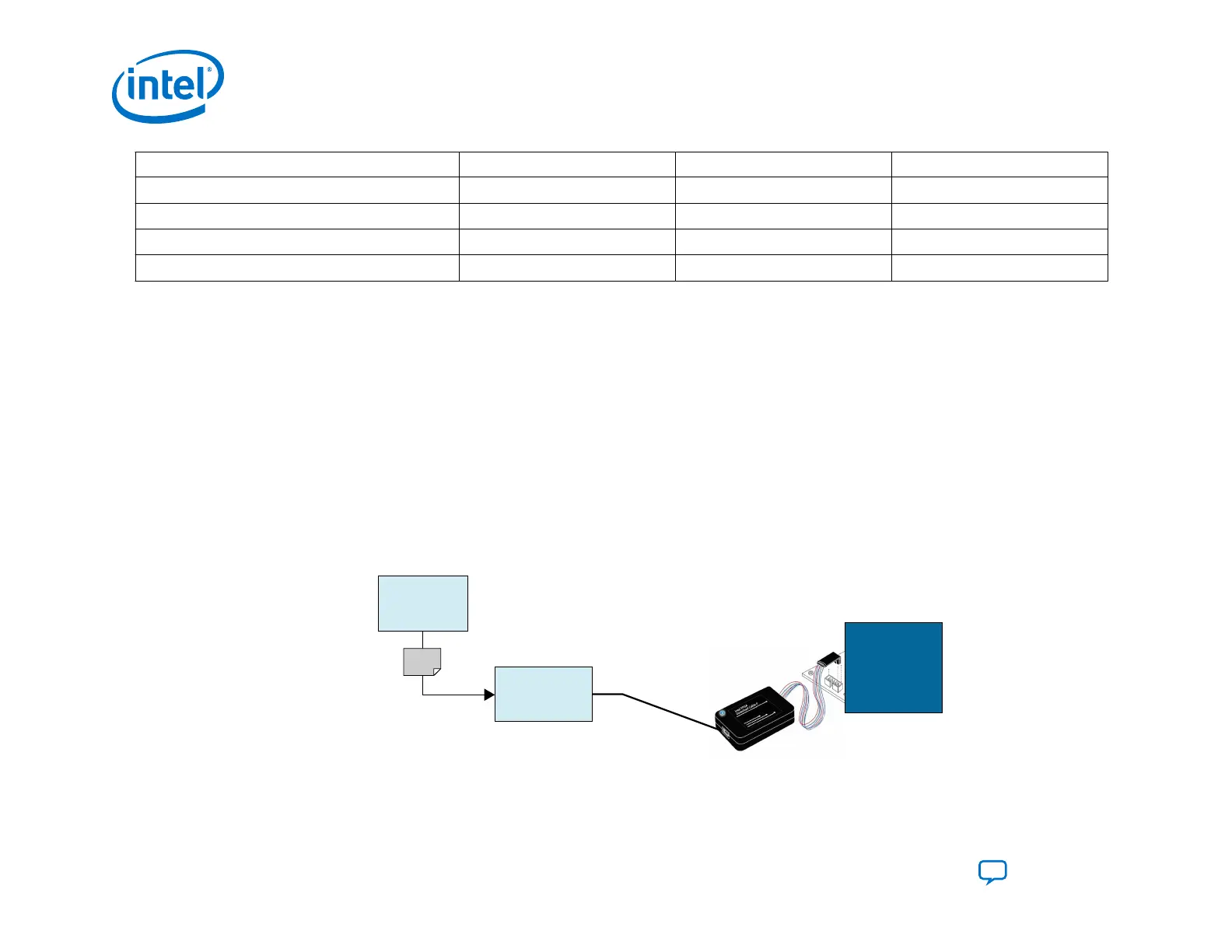

The following figure illustrates JTAG programming. This is the simplest device configuration scheme. You do not have to use

the File ➤ Programming File Generator to convert the .sof file to a .pof.

Figure 48. JTAG Configuration Scheme

Quartus Prime

Compilation

JTAG

Programmer

Quartus Prime

Programmer

SOF

Intel FPGA

3. Intel Agilex Configuration Schemes

UG-20205 | 2019.10.09

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

114

Loading...

Loading...