2.3. Reset Release Intel FPGA IP

Intel requires that you either use the Reset Release Intel FPGA IP or the INIT_DONE signal routed back in through a pin to

hold your design in reset until configuration is complete.

The Reset Release Intel FPGA IP is available in the Intel Quartus Prime Software. This IP consists of a single output signal,

nINIT_DONE. The nINIT_DONE signal is the core version of the INIT_DONE pin and has the same function in both FPGA First

and HPS First configuration modes. Intel recommends that you hold your design in reset while the nINIT_DONE signal is high

or while the INIT_DONE pin is low.

When you instantiate the Reset Release IP in your design, the SDM drives the nINIT_DONE signal. Consequently, the IP does

not consume any FPGA fabric resources, but does require routing resources.

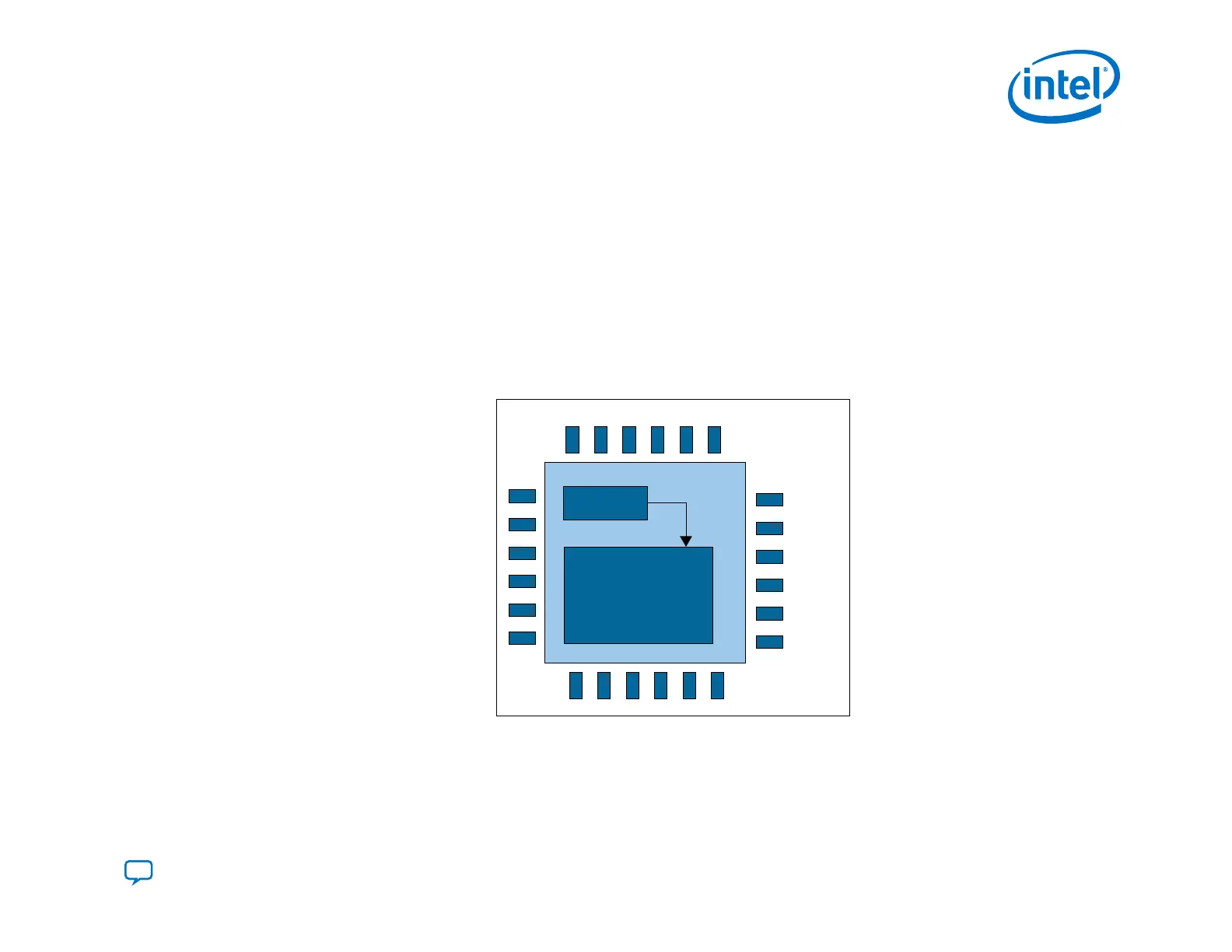

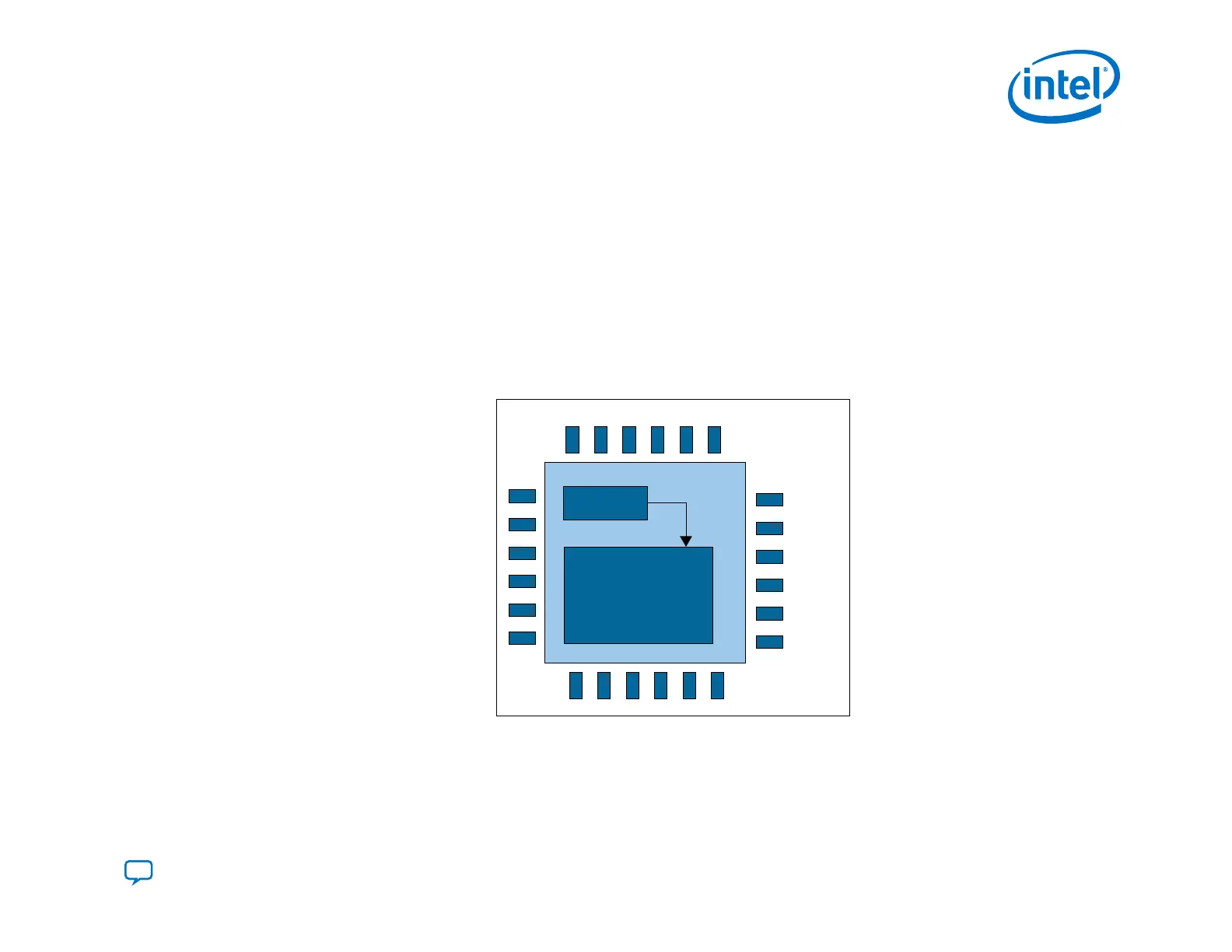

Figure 6. Reset Release Intel FPGA IP nINIT_DONE Internal Connection

Board

nINIT_DONE

Reset

Application Logic

Intel FPGA

Reset Release IP

2. Intel Agilex Configuration Details

UG-20205 | 2019.10.09

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

23

Loading...

Loading...