4.6.6. Removing an Application Image

1.

Set up exclusive access to the AS x4 interface and flash memory by running the QSPI_OPEN and QSPI_SET_CS

commands in the Tcl Console window.. You now have exclusive access to the AS x4 interface and flash until you relinquish

access by running the QSPI_CLOSE command. Write the new application image to the flash memory using the

QSPI_WRITE command.

2.

Write 0x00000000 to the application image start address stored in the image pointer entry of the configuration firmware

pointer block (CPB0 and CPB1) using the QSPI_WRITE command.

Note: You must update both copies (copy0 and copy1) when editing the configuration firmware pointer block and sub-

partition table.

3.

Erase the application image content in the flash memory using the QSPI_ERASE command.

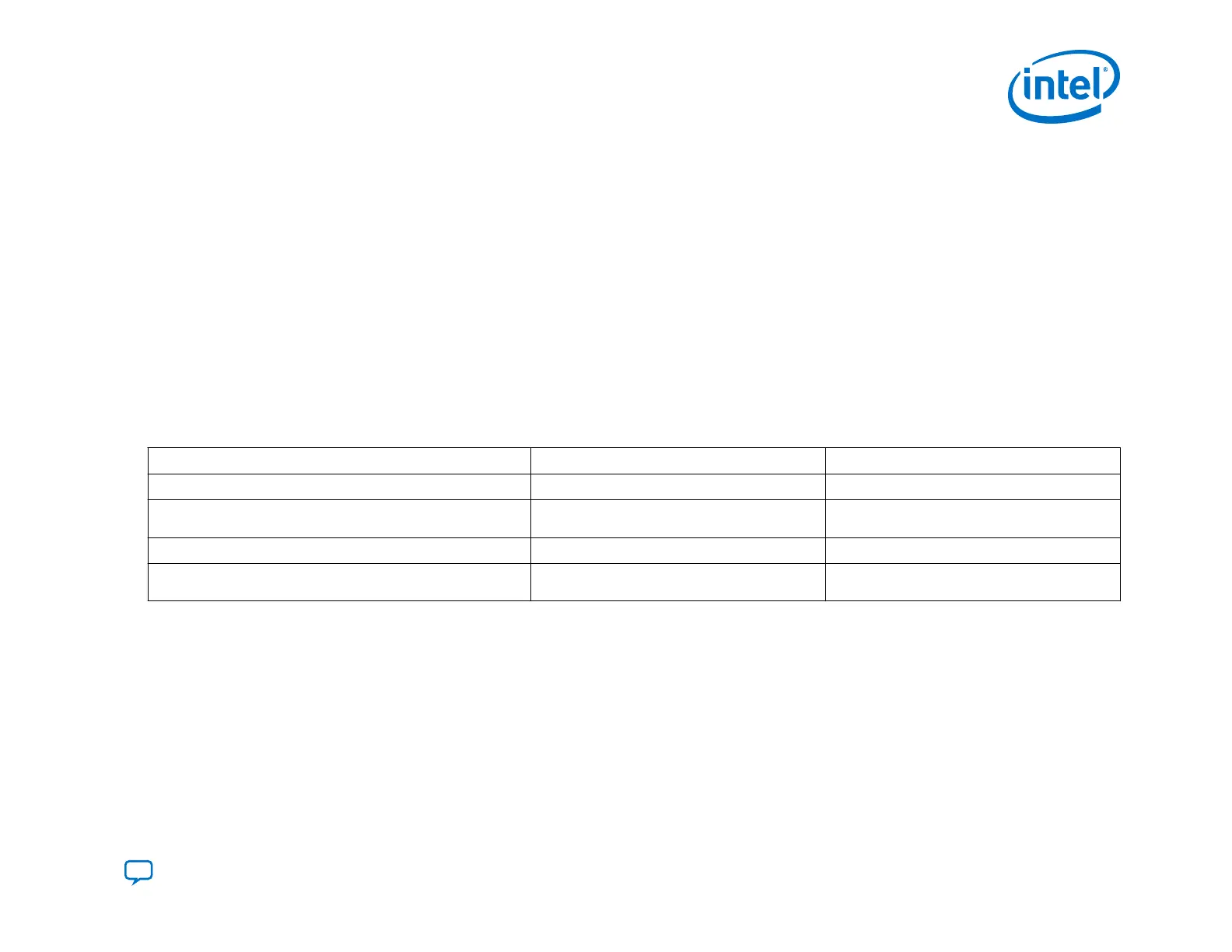

4. To remove a new application image, add another new application image in the next or subsequent image pointer entry or

allow the device to fall back to the previous or secondary application image in your application image list. The following

table shows correct entries for image pointer entries for CPB0 and CPB1 for offsets 0x20 and 0x28 :

CPB Start Address + 0x20

Content Value

CPB0 + 0x20 = 0x002E4020

Old application image pointer entry (lower priority)

0x002F4000

CPB0 + 0x28 = 0x002E4028

Current/new application image pointer entry

(highest priority)

0x03FF0000

CPB1 + 0x20 = 0x002EC020

Old application image pointer entry (lower priority)

0x002F4000

CPB1 + 0x28 = 0x002EC028

Current/New application image pointer entry

(highest priority)

0x03FF0000

4. Remote System Update (RSU)

UG-20205 | 2019.10.09

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

177

Loading...

Loading...