SDM Pins MSEL Function Configuration Source Function

Avalon-ST x8 AS x4

SDM_IO14

—

AVSTx8_CLK

—

SDM_IO15

—

AVSTx8_DATA6

—

SDM_IO16

— — —

2.5.2. MSEL Settings

After power-on MSEL[2:0] pins specify the configuration scheme for Intel Agilex devices. Use 4.7-kΩ resistors to pull the

MSEL[2:0] pins up to V

CCIO_SDM

or down to ground as required by the MSEL[2:0] setting for your configuration scheme.

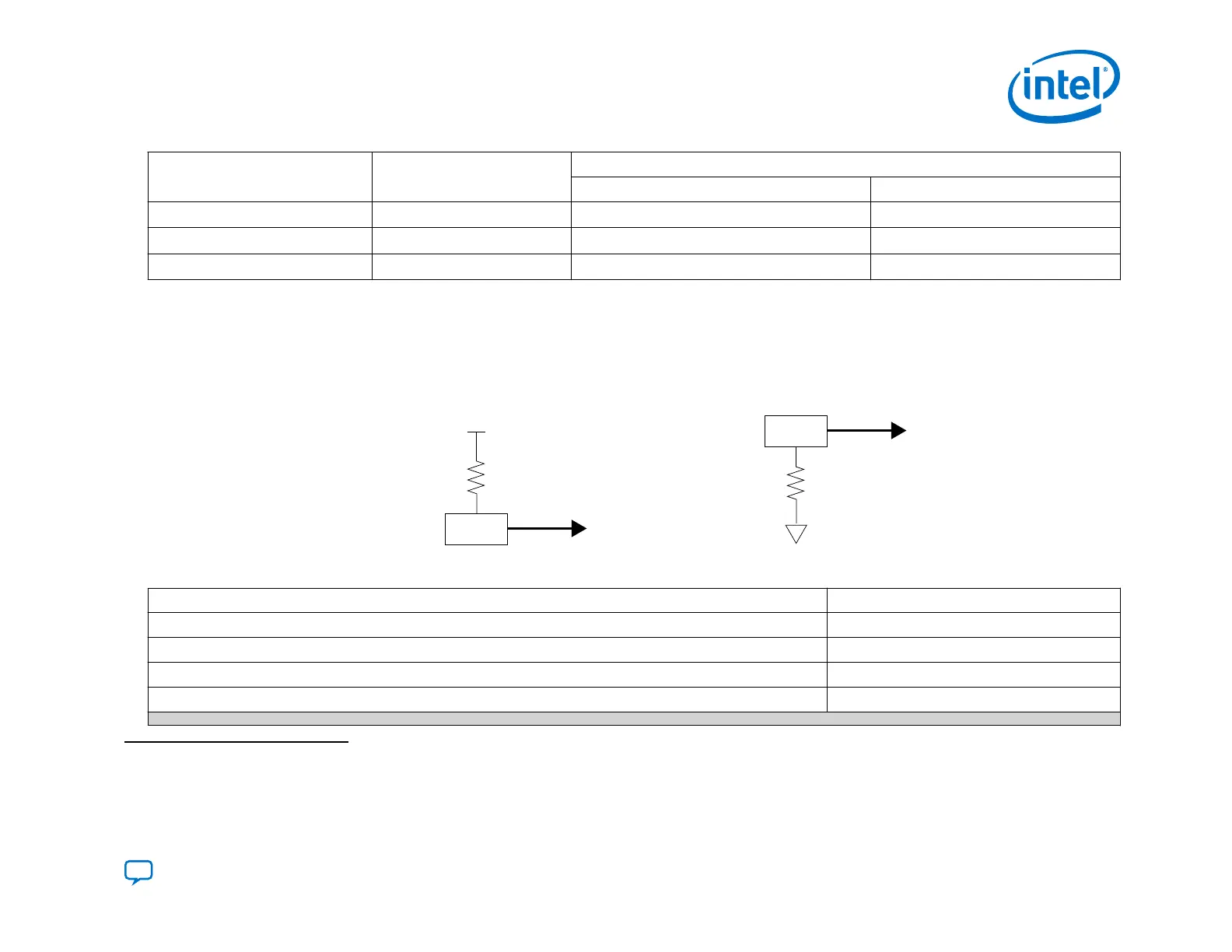

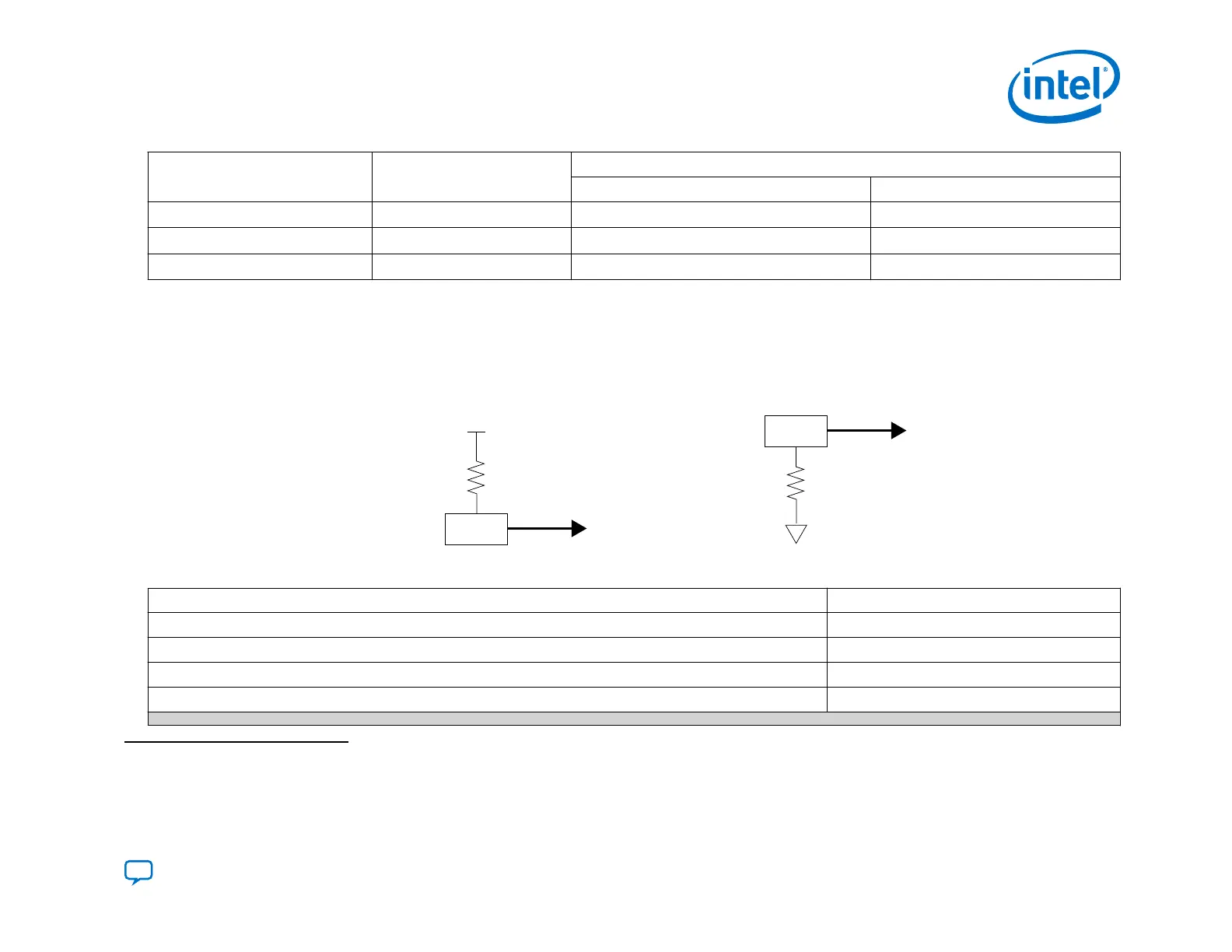

Figure 8. MSEL Pull-Up and Pull-Down Circuit Diagram

RUP

VCCIO_SDM

MSEL[0]

4.7kΩ

RDN

MSEL[0]

4.7kΩ

OR

Table 4. MSEL Settings for Each Configuration Scheme of Intel Agilex Devices

Configuration Scheme MSEL[2:0]

Avalon-ST (x32) 000

Avalon-ST (x16) 101

Avalon-ST (x8) 110

AS (Fast mode – for CvP)

(2)

001

continued...

(2)

If you use AS Fast mode and are not concerned about 100 ms PCIe linkup, you must still ramp the V

CCIO_SDM

supply within 18 ms.

This ramp-up requirement ensures that the AS x4 device is within its operating voltage range when the Intel Agilex device begins to

access it.

2. Intel Agilex Configuration Details

UG-20205 | 2019.10.09

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

27

Loading...

Loading...