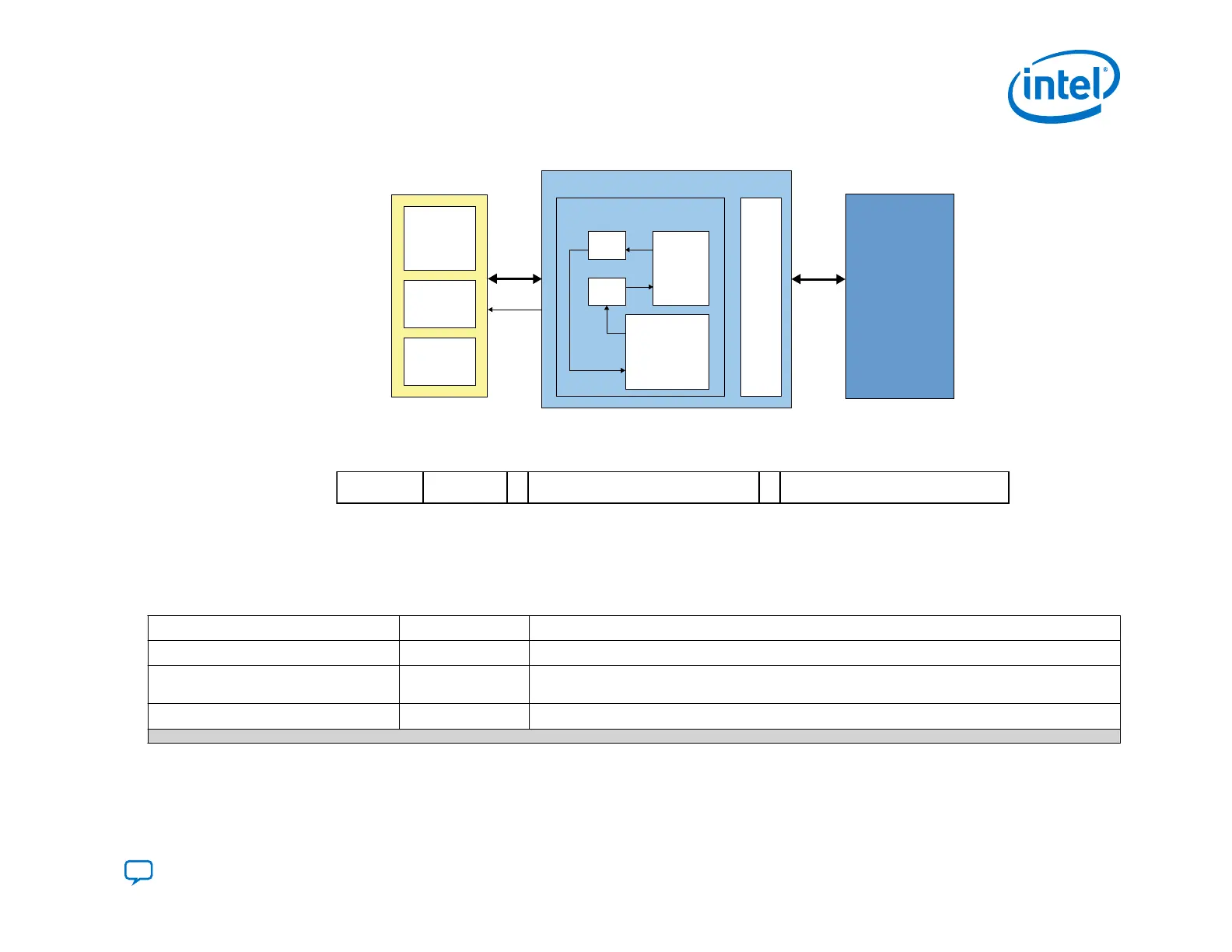

Mailbox Client Role

Avalon-MM

Interface

IRQ

SDM

Communication

Hub

Mailbox

Driver

Secure

Device

Manager

Avalon-ST

Interface

Host Controller

FPGA Core Fabric

Controller

FIFO

FIFO

JTAG

to

Avalon Master

Processor

Custom

Logic

Nios II

Mailbox Client Intel FPGA IP

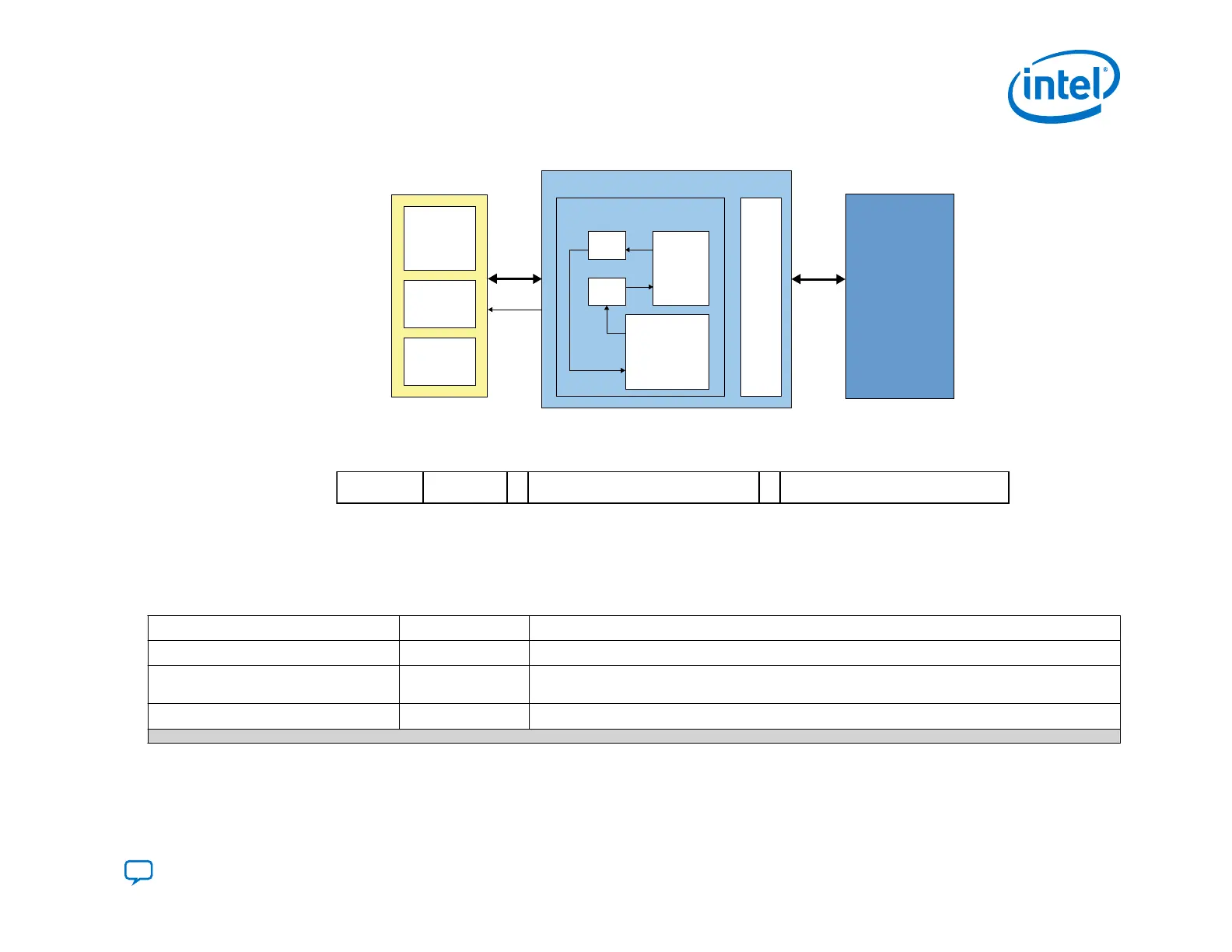

Figure 58. Command and Response Header Format

31 30

RESERVED ID 0 0 COMMAND / ERROR CODELENGTH

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Note: The LENGTH field in the command header must match the command length of corresponding command.The following table

describes the fields of the header command. Your client must read all the response words, even if your client does not

interpret all the response words.

Table 34. Mailbox Client Intel FPGA IP Command and Response Header Description

Header Bit Description

Reserved [31:28] Reserved.

ID

[27:24] The command ID. The response header returns the ID specified in the command header. Set different

IDs in each command to match responses with commands.

0

[23] Reserved.

continued...

4. Remote System Update (RSU)

UG-20205 | 2019.10.09

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

133

Loading...

Loading...